# Committed to Innovation, Leti Creates Differentiating Solutions for its Industrial Partners.

eti is a research institute of CEA Tech and a recognized global leader in miniaturization technologies. Leti's teams are focused on developing solutions that will enable future information and communication technologies, health and wellness approaches, clean and safe energy production and recovery, sustainable transport, space exploration and cybersecurity.

For 50 years, the institute has built long-term relationships with its industrial partners, tailoring innovative and differentiating

solutions to their needs. Its entrepreneurship programs have sparked the creation of 64 start-ups. Leti and its industrial partners work together through bilateral projects, joint laboratories and collaborative research programs.

Leti maintains an excellent scientific level by working with the best research teams worldwide, establishing partnerships with major research technology organizations and academic institutions. Leti is also a member of the Carnot Institutes network\*.

\*Carnot Institutes network: French network of 34 institutes serving innovation in industry.

CEA Tech is the technology research branch of the French Alternative Energies and Atomic Energy Commission (CEA), a key player in research, development and innovation in defense & security, nuclear energy, technological research for industry and fundamental physical and life sciences.

www.cea.fr/english

# Leti at a glance

€315

million budget

800 publications per year

ISO 9001 certified since 2000

Founded in

1967

Based in

France (Grenoble) with offices in the

USA (Silicon Valley)

and Japan (Tokyo)

350 industrial partners

1,900 researchers

2,760 patents in portfolio

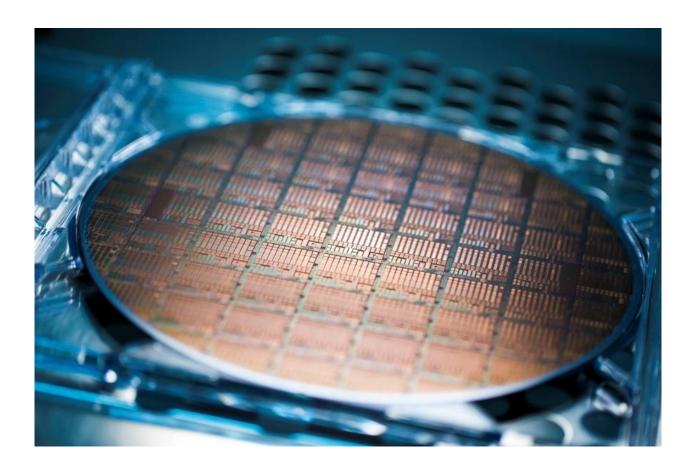

91,500 sq. ft. cleanroom space, 8" & 12" wafers

64 startups created

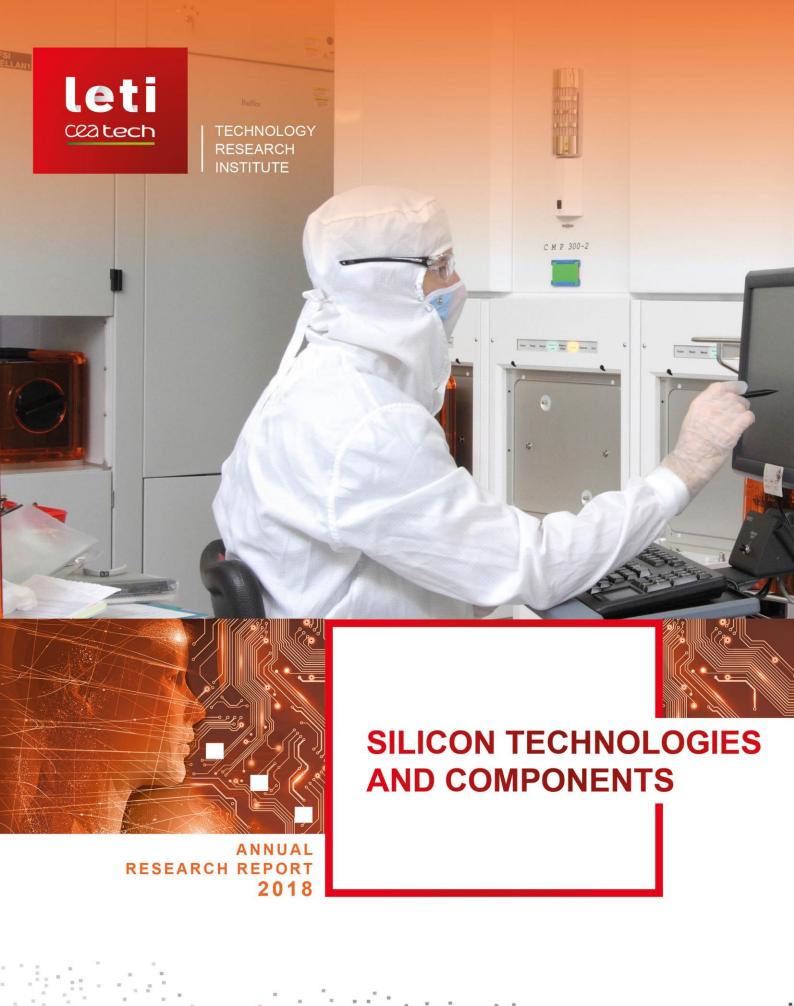

# SILICON TECHNOLOGIES AND COMPONENTS

Within CEA Tech and Leti, silicon technologies and components research activities are shared between two divisions gathering together around 600 researchers:

The Silicon Technologies Division carries out innovative process engineering solution and research, operates 24/7 year round, 7500m2 of state-of-the-art cleanroom space divided into three different technology platforms.

The Silicon Components Division carries out research on nanoelectronics and heterogeneous integration on silicon and is focusing on two mains areas: on-going shrinking of CMOS devices to extend Moore's Law for faster, less-expensive computing power, and the integration of new capabilities into CMOS, such as sensors, power devices, imaging technology, and new types of memory, to enable new applications.

This booklet contains 48 one-page research summaries covering advances in the focus areas of our Silicon Devices and Technologies Divisions, highlighting new results obtained during the year 2018.

# CONTENTS

| EDITO                                               | 07 |

|-----------------------------------------------------|----|

| KEY FIGURES                                         | 11 |

| SCIENTIFIC ACTIVITY                                 | 15 |

| 01 / Core & beyond CMOS                             | 17 |

| 02 / Memories                                       | 27 |

| 03 / Patterning                                     | 33 |

| 04 / MEMS, NEMS & RF Components                     | 41 |

| 05 / Power & Energy                                 | 51 |

| 06 / Emerging Materials & Processes                 | 59 |

| 07 / 3D Integration & Packaging                     | 69 |

| 08 / Physical-Chemical Characterization & Metrology | 75 |

| 09 / PHD Degree awarded                             | 87 |

# **EDITO**

Laurent Clavelier, Head of Technological platforms

Dear Reader,

2018 was a very rich year in terms of results, investments and organization. It was the year we decided to launch our ambitious plan for 300mm technology autonomy for the CEA-LETI. This investment plan covers a period of 4 years.

Starting in 2018, we acquired a new lithography capability with a 193mm immersion scanner. Today this scanner is in operation and performing advanced lithography since October 2018 on CMOS, memories and photonic demonstrators. The next step of the plan is in progress with a focus on tools that are essential for ST and SOITEC programs: substrates, nonvolatile memories and imagers.

All this infrastructure and associated programs are important for our scientific activities. Since 300mm tools are the most advanced in term of performances, they are unique in allowing us to explore new areas and phenomena with the ability to integrate directly on real devices. To do that, a strong scientific understanding, and thus strong scientific positioning, is mandatory.

In terms of scientific results, I would like to thank our teams for their impressive achievements: 100 abstracts accepted at international conferences; 100 peer reviewed journal papers accepted; 9 ANR and 6 EU projects submitted to support our most advanced activities. We have also generated 42 patents.

Epitaxy of IV, II-V and II-N materials, CMP, molecular bonding, advanced and alternative lithography (nanoimprint, DSA), 2D materials, materials for nonvolatile memories, advanced metrology and characterization, ... are some of the domains in which we are strongly involved and in which we will reinforce our activity. All this is possible because we collaborate with our colleagues from the applicative divisions and academic laboratories in France (CEA fundamental research, CNRS-LTM, IEMN, CEMES, ...) but also in the EU and across the world (FhG, IMEC, Stanford, Caltech, ...).

To finish, I would like to welcome a new activity to our division: material and technology activities for photonics (II-VI and III-V) have just joined us in January 2019. The scientific activity and knowledge of these laboratories rely on a solid and long term expertise. Thus, cross fertilization with IV material activities are expected in 2019!

# **EDITO**

Pascale Berruyer, Head of Silicon Components

Dear Reader,

Today, societal needs in terms of wellness, mobility, communication, and ubiquitous services are driving the rapid evolution of microelectronic technologies. High performance computing, advanced RF communications, power electronics and advanced sensors are key elements for AI, 5G communications, IoT, autonomous driving, hybrid and electrical vehicules. With the central mission to efficiently develop the related advanced hardware, the Silicon Components Division is at the heart of all these societal demands, broadly relying upon state-of-the-art 300 and 200 mm facilities. These facilities allow our experts to continuously assess disruptive technologies and federates global partnerships for an efficient industrial manufacturing of these solutions. Significant successes have been achieved in 2018 in the fields of advanced nanoelectronics, power electronics and sensors.

Just to highlight few of them, let me mention:

- -the important Léti support to industrialization of FDSOI which has now reached its maturity.

- -the achievement of major breakthroughs in 3D sequential technology CoolCubeTM.

- -the rise of quantum activities in partnership with CEA-INAC and Néel institute, and particularly the implementation of a technology platform mixing Qbits devices and CMOS electronic control. An ERC Synergy grant has just been obtained to also support this activity.

- -the collaboration with STMicroelectronics Crolles to develop next generations of PCM embedded non-volatile memories addressing automotive and smartcard markets.

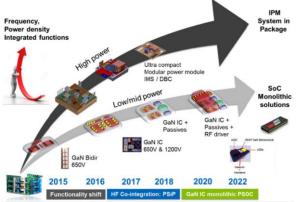

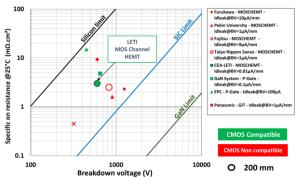

- -the increasing partnership with STMicroelectronics Tours and Catane through IRT/Nanoelec and IPCEI-Nano2022 programs on diodes and power transistors on GaN on Si, with a maturity 10 achieved on 650V diodes.

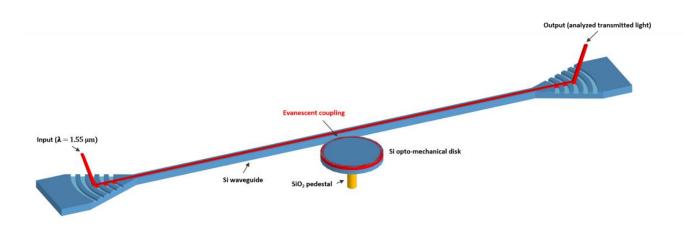

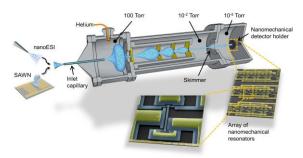

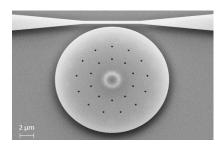

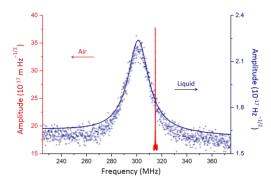

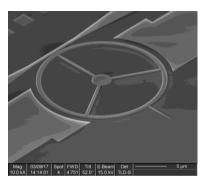

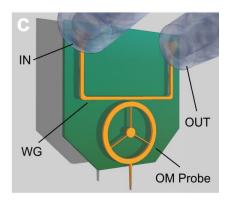

- -the implementation of new concepts for environmental and biological sensors, especially based on optomechanical nanoresonators.

It is worth noting that most of the highlighted successes have been achieved in the frame of outstanding bilateral partnerships and with the sustained efforts of our team that I would like to sincerely thank here.

I hope you will enjoy reading the overview of these achievements.

# **EDITO**

Jean-Charles Barbé & Raluca Tiron

Chief Scientists

We are proud to release our eighth Silicon Components and Technologies Annual Scientific Research Report, for the year 2018. This booklet contains 48 one-page research summaries covering advances in the focus areas of our Silicon Components and Technologies Divisions, highlighting new results during the year.

The year 2018 illustrates the continuing innovation of our Si technologies divisions to contribute from a hardware point of view to the big data and artificial intelligence area, Internet of Things (IOT), automotive, energy, health and environment monitoring.

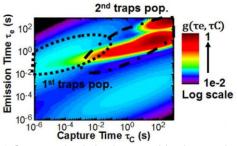

In this annual report, we confirmed our positioning in disruptive Si research with several highlights including quantum computing development on Si CMOS, neuromorphic architecture with emerging resistive memories, reduced programming consumption in RRAM arrays, innovative back-end selectors for memories, disruptive 3D concept or advanced mask-less pattering, opto-mechanic resonators, RF switches concepts with emerging materials, advanced GaN-on-Si for power electronics.

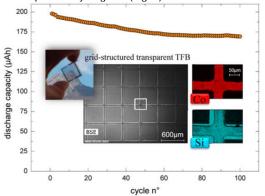

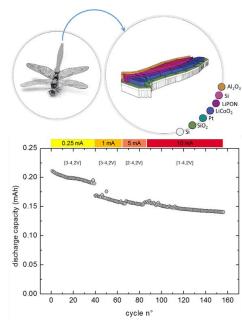

Our research on future IoT sensing systems includes new transducers, embedded RF functionalities and substrates, embedded intelligence, dedicated packaging, energy harvesters and micro-batteries.

In 2018, the Silicon Divisions produced 403 publications, achieving impact factors as high as 41.

We thank our industrial partners for their continuing confidence in us. We are committed to ensuring the transfer of the most advanced research to industry. Strong industrial partnerships are the foundation of our culture of innovation.

We are committed in international scientific collaborative research by participating in major european research programs, European Research Council grants, international conferences, program committees, boards of governors and evaluation committees.

Underlying all these efforts is the cooperation of all our researchers and management, as well as the Silicon Technologies and Components Divisions and CEA-LETI's scientific advisory board.

We also wish to extend my appreciation to the 11 chapter's editors and authors of the 2018 Scientific Report, who spared no effort to prepare this document.

# **KEY FIGURES**

498 researchers

135 industrial residents

498 PhD students in 2018

12 Post-docs in 2018

200 & 300 mm platforms for advanced CMOS/3D

250 tools for 200 mm, non stop operation

140 tools for 300 mm, non stop operation

6100 m<sup>2</sup> cleanroom ISO3-5

200 mm platforms for MEMS

130 tools, non stop operation

2200 m<sup>2</sup> cleanroom ISO4-

122 commun laboratories

124 patent filed in 2017

**403** papers issued in 2017 (WOS, SCOPUS)

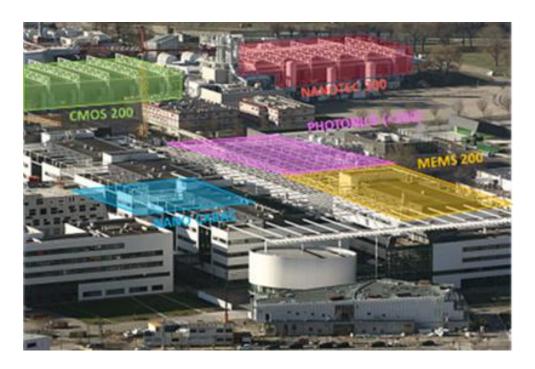

#### **TECHNOLOGICAL PLATFORMS**

**The silicon divisions** operate 8300 m<sup>2</sup> of state-of-the-art cleanroom space divided into three platforms, gathering 500 process tools and a combined staff of more than 450; they run industry-like operations, 24 hours a day, 7 days a week, all year round.

- The 300 platform provides 300mm wafer processing, which can be applied to both semiconductor and microsystem devices.

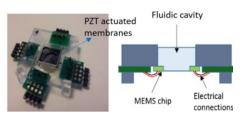

- The 200mm platform produces non-CMOS Micro-ElectroMechanical Systems (MEMS).

Both platforms are focused on the More than Moore initiative to develop new semiconductor capabilities. An innovative cleanroom shuttle system links the two platforms to add process flexibility and faster processing.

The multi-scale platform for imagers and IR applications.

All research carried out in our cleanrooms benefits from the Nano-Characterization Platform, which is located on the MINATEC campus. This platform, unique in Europe, covers eight domains of competencies, including electron microscopy, X-ray diffraction, ion beam analysis, optics, scanning probe, surface analysis and sample preparation, magnetic resonance.

#### **ORGANIZATION**

#### Silicon Technologies Division is organized according to six departments.

- Three Process Departments whose missions are to execute generic process steps for all projects and to develop innovative processes to provide state-of-the-art solutions to internal and external customers. These departments are focused on patterning, deposition, and surface treatments. Their research activities in collaboration with key universities will support Leti's advanced position in the future.

- A Characterization Department whose mission is to perform off-line observations to characterize process steps, materials or components. This department also has a research activity to maintain its level of excellence.

- Two Support Departments: one is in charge of the planning, the interface with internal divisions or external customers as well as methods, training and clean-concepts. The other is responsible for facilities operations and engineering.

**Silicon Components Division** is organized around three departments with clear objectives and market focus.

- Memory and compute mission is to simulate, model, develop, demonstrate and test new generations of circuits and modules for sub-20nm CMOS, digital and memory.

- Sense and Act Department designs and develops innovative microsystem components (sensors, actuators) and the associated toolbox (packaging, heterogeneous integration, reliability).

- Power Energy and Connectivity Department develops and demonstrates technology modules and components for power and energy (photovoltaic, power electronics, RF, integrated storage)

# **SCIENTIFIC ACTIVITY**

#### **Publications**

178 publications in 2018 (WoS, SCOPUS)

225 international conference communications.

#### Prize and awards

G. Poupon, 2018 IEEE EPS Regional Contributions Awards

M. Kazar Mendes, Best Poster Award EMRS, Spring meeting 2018

M. Moreno Villavicencio , Best Student Award, AVS 65th, 2018

J.M. Hartmann, ECS Appreciation Award, AIMES 2018

M. Mastari, Best student paper award, ECS Cancun Oct. 2018

F. Andrieu, Prix Brillouin-Glavieux 2018

A. Verdy, Best student paper award IMW 2018

R. Alhalabi, Best poster award, NVMTS2018

V.Enyedi, Best poster award. Spectratome 2018

2 on-going European Research Council Grants (S. Hentz, D. Cooper)

2 newly-started European Research Council Grants (F. Andrieu, M. Vinet)

#### Experts

7 International Experts, 4 Research Directors, 38 Senior Experts, 56 Experts, 26 of them holding an HDR.

#### Scientific committees

- National Research Agency committee.

- Technical Program committees of: IEEE-IEDM, IEEE-VLSI, IEEE S3S, IEEE ESSDERC, IEDM IEEE-IITC, MAM ECS AIMES – SiGe symposium ECS AIMES – Bonding symposium SPCC, ICSI-ISTDM,ICPT ICMOVPE, Waferbond

AMC, ECS Transactions AIMES, JNTE, AVS, SPIE Advanced Lithography, SISC, SSDM, ICICDT, MRS, IMW Scientific comitee for (Collaborative Research Group) Françaises de l'ESRF

# **Conferences and Workshops organizations**

G03 SiGe Symposium at AIMES, DSA Symposium, PESM, 2nd workshop of the European FIB Network

# International Collaborations

Forschung Zentrum Juelich (Germany), Stanford University (USA), Caltech (USA), The University of California (USA), Fraunhofer institutes (Germany), Università degli Studi di Ferrara (Italy) University of Cambridge (GB), Université Catholique de Louvain (Belgium),

Politecnico Di Milano (Italy),

Paul Scherrer Institute (Switzerland), École Polytechnique Fédérale de Lausanne (Switzerland), ETH – Zürich (Switzerland), CNR (Italy),

University of Chicago (USA), Sherbrooke, University (Canada) NIMS (Japan),

University of Southern Denmark University Cagliari (Denmark), Institute for Technical Physics and Materials Science (Budapest),

Hungarian Academy of Sciences (Budapest), Korea University (Seoul) Centro universitario FEI (Brazil),

University of Tsukuba (Japan).

# O1 CORE & BEYOND CMOS

- Integration of Spin Quantum Bits in Silicon MOS Technology

- Breakthroughs in 3D Sequential Technology

- Towards a High Performance and Reliable 3D Sequential Integration

- Low Temperature Epitaxy and Clean for CoolCube<sup>™</sup> Integration

- Advanced FDSOI CMOS: Strain Optimization and Design Technology co-Optimization

- Recent Bulk Modelling Development on PSP Model and Prospective Modeling of Single Event Transients.

- Strain Maps And Tunability of Parasitic Channel in Gate-All-Around Stacked Nanosheets FETs

# **Integration of Spin Quantum Bits** in Silicon MOS Technology

40.0

#### **RESEARCH TOPIC:**

Quantum information, spin, qubits, silicon, CMOS

#### **AUTHORS:**

Louis Hutin, Benoit Bertrand, Vincent Mazzocchi, Jean-Michel Hartmann, Maud Vinet (Yann Michel Niquet, Tristan

#### **ABSTRACT:**

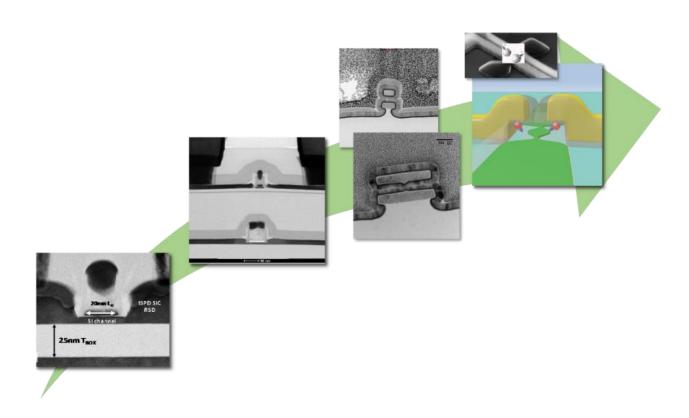

We fabricated Si Quantum Dot (QD) devices using relatively minor adaptations of a standard SOI CMOS process flow. We demonstrated that the spin of confined charges could be controlled via a local electrical-field excitation, owing in the case of electrons to a geometrically-enabled tuning of the valley splitting and inter-valley spin-orbit coupling. Furthermore, we investigated improvement paths such as extending the spin coherence time by using epitaxially-grown layers of nuclear-spin-free <sup>28</sup>Si (99.992%) as a device template, and developing novel 3D architectures compatible with topological quantum error correction schemes.

SCIENTIFIC COLLABORATIONS: CEA-IRIG, CNRS Institut Néel

#### **Context and Challenges**

We aim to engineer devices for the coherent manipulation of information encoded as a quantum superposition of basis states, i.e. quantum bits (qubits). In particular, the qubit state is mapped to the spin of a charged particle confined in a Quantum Dot (QD). In our case, holes or electrons are accumulated below MOS Gates wrapping around mesa-etched Si NanoWires (NW), forming 1D arrangements of nearest neighbor-coupled QDs. Coherent control and dispersive readout of hole spin qubits were recently demonstrated in such CMOS-compatible devices. We continue to explore ways to improve quantum information fidelity through developing control schemes, material engineering and

#### **Main Results**

Surprisingly, we observed spin transitions in MOS Gate-confined electrons using only E-field excitations. The underlying mechanism is based on the interplay between Spin-Orbit Coupling (SOC) and the multi-valley structure of the Si Conduction Band, and is enhanced by the "Corner QD" device geometry. We also showed that by offering the ability to break and restore the confinement symmetry at will, the SOI Back-Gate may allow fast programming in valley mode, and stable information storage in spin mode [1]. This functionality could alleviate the trade-off between fast manipulation and long coherence time, thereby improving the outlook for compact, scalable and fault-tolerant quantum logic circuits.

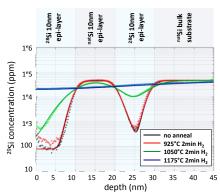

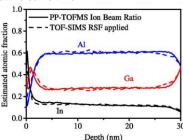

Hyperfine interactions with nuclear spins in the host crystal can limit the coherence time of an electron spin qubit. The most abundant Si isotope (28Si: 92.23%) carries no nuclear spin, but <sup>29</sup>Si (4.67%) does. We have grown epilayers with a <sup>28</sup>Si isotopic purity greater than 99.992% on 300 mm diameter natural abundance silicon (natSi) crystals (Fig. 1). The quality of the mono-crystalline isotopically purified epilayer conforms to the same drastic quality requirements as the natural epilayers used in our pre-industrial CMOS facility [2].

Figure 1: SIMS data (symbols) and simulation results (lines) of <sup>29</sup>Si concentration depth profile vs. annealing conditions in a <sup>28</sup>Si 10nm / natSi 10nm / 28Si 10nm / bulk natSi stack [2].

#### **Perspectives**

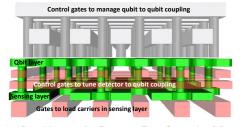

Motivated by topological compatibility with Quantum Error Correction (QEC) codes, disruptive architecture proposals have emerged recently, relying on crossbar addressing of 2D arrays of QDs. Our own 3D architecture (Fig. 2) features a large 2D array of Si QDs with line/column control of their tunnel coupling to the nearest neighbors. It is also coupled to a lower tier of Si QDs enabling fast initialization and readout.

Figure 2: 3D architecture for Quantum Error Correction [3].

- [1] L. Hutin et al., VLSI Tech. Symp. 2018, <u>10.1109/VLSIT.2018.8510665</u>

- [2] V. Mazzocchi et al., J. Crystal Growth, 2018, <u>10.1016/i.jcrysgro.2018.12.010</u> [3] M. Vinet et al., IEDM 2018, <u>10.1109/IEDM.2018.8614675</u>

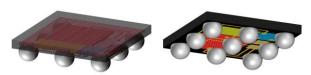

# **Breakthroughs in 3D Sequential Technology**

#### **RESEARCH TOPIC:**

3D sequential, CoolCube, low thermal process, gate stack, iBEOL, Smart Cut

#### **AUTHORS:**

C. Fenouillet-Beranger, L. Brunet, P. Batude, N. Rambal, F. Ponthenier, E. Arnoux, F. Andrieu, M. Vinet (J. Aubin, J-B. Pin)

#### **ABSTRACT:**

The 3D sequential integration, of active devices requires the thermal budget of top tier processing to be limited to 500°C in order to ensure the stability of the bottom devices. Here we present breakthroughs in six areas that were previously considered as potential showstoppers for 3D sequential integration from either a manufacturability, reliability, performance or cost point of view. Our experimental data demonstrate the ability to obtain 1) low-resistance poly-Si gate for the top FETs, 2) Full low-temperature RSD epitaxy 3) Stability of intermediate BEOL (iBEOL), 4) Stable bonding above ULK, 5) Efficient contamination containment for wafers with Cu/ULK iBEOL enabling their re-introduction in FEOL for top FET processing 6) Smart Cut™ process above a CMOS wafer.

SCIENTIFIC COLLABORATIONS: STMicroelectronics (France), AMAT (France), SCREEN-LASSE (France)

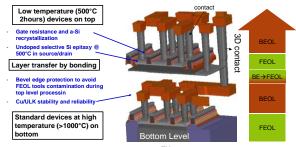

#### **Context and Challenges**

3D-monolithic or 3D sequential CMOS technology is based on stacking active device layers on top of each other with very small 3D contact pitch (similar pitch as standard contact). However, such an integration process faces the challenge of fabricating high-performance devices in the top tier without degrading the electrical characteristics of the bottom tier. Therefore, limiting the thermal budget to 500°C is mandatory. Owing to in-depth and exhaustive experimental studies, our previous work has highlighted two critical processing issues: i) Low-temperature gate stack integration ii) Low-temperature selective epitaxy of silicon on source and drain. In parallel we recently demonstrated for the first time the integration of low temperature SiCO spacer material deposited at 400°C in both standard (High temperature) and low temperature (LT) anneal CMOS FDSOI process flow [1]. This work presents advances bringing 3D sequential integration closer to manufacturability. Here we present six achievements on process steps that were considered as potential showstoppers for this technology (Fig.1).

#### **Main Results**

In order to obtain high performance top FETs, low gate access resistance has been achieved using UV nano-second laser recrystallization of in-situ doped amorphous silicon [2]. Full 500°C selective Si epitaxy process is demonstrated owing to an advanced LT surface preparation with a combination of dry and wet etch preparation; the selective epitaxial growth is obtained with the cyclic use of a new Si precursor and Cl2 etching.

In parallel, this work paves the way to manufacturability of 3D sequential integration including iBEOL with standard ULK and Cu metal lines. A bevel edge contamination containment strategy composed of 3 steps (bevel etch, decontamination, encapsulation) enable wafers re-introduction in FEOL environment after BEOL process. In addition, the stability of line to line breakdown voltage for interconnections submitted to 500°C anneals is demonstrated for the first time.

Finally, Smart  $\text{Cut}^{\text{TM}}$  transfer of a crystalline silicon layer on a processed bottom level of FDSOI CMOS devices is demonstrated as an alternative to SOI bonding and etch back process scheme for top channel fabrication (Fig.2).

Figure 1: 3D sequential Coolcube™ integration and remaining process issues.

Figure 2: STEM cross-section after layer transfer by Smart Cut<sup>TM</sup> process and thinning above a 20nm gate length transistor (left). The corresponding photography of layer transfer above CMOS.

#### **Perspectives**

A full low temperature 500°C devices integration is ongoing for the top level of the CoolCube™ integration.

- [1] C. Fenouillet-Beranger et al., SSDM, 2018, <a href="https://confit.atlas.jp/quide/event/ssdm2018/subject/B-6-02/advanced">https://confit.atlas.jp/quide/event/ssdm2018/subject/B-6-02/advanced</a> [2] L. Brunet et al., IEEE IEDM, 2018, <a href="https://confit.atlas.jp/quide/event/ssdm2018/subject/B-6-02/advanced">https://confit.atlas.jp/quide/event/ssdm2018/subject/B-6-02/advanced</a>

## **Towards a High Performance and Reliable 3D Sequential Integration**

#### **RESEARCH TOPIC:**

3D sequential integration, low thermal budget process flow, transistor reliability

#### **AUTHORS:**

X. Garros, A. Tsiara, L. Brunet, P. Batude, C. Fenouillet-Béranger (G. Ghibaudo)

#### **ABSTRACT:**

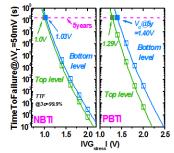

LETI demonstrates not only great performance but also excellent reliability of a 3D sequential integration scheme. We highlight, for the first time, that the top level transistor can be successfully processed at 630°C with almost no impact on the performance and reliability of the bottom level. Key properties of the gate stack like EOT and leakage current are preserved as well its immunity to trapping. We also prove that these top level devices made at low temperature can already meet key reliability requirements as DC 5 years BTI lifetime. Finally an example of successful and robust 3D logic integration is proposed based on a 3D inverter combining a top-level PMOS with a bottom-level NMOS. This work gives pathways towards a reliable 3D sequential technology.

**SCIENTIFIC COLLABORATIONS: IMEP-LAHC**

#### **Context and Challenges**

3D Sequential CoolCube™ integration is based on stacked layers of devices fabricated one on top of each other, allowing extremely scaled 3D contact pitch [1]. However the fabrication of the two level transistors faces many integration challenges. Amongst them, reliability remains a key issue. Actually the top transistor must be processed at low temperature in order to preserve the integrity of bottom level MOSFET and BEOL levels. However, using a low thermal budget may reduce the top device performance by increasing access resistance and/or decreasing channel carrier mobility. It may be also detrimental for the gate oxide reliability because the curing of microscopic defects responsible for trapping is less effective at lower temperature. However, it is still unclear if a 3D sequential integration can be reliable enough since, so far, no study has addressed the reliability concern in a true 3D sequential technology.

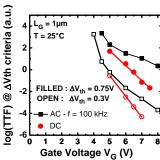

#### Main Results

The purpose was therefore to propose an in-depth analysis of both performance and reliability of a 630°C fully integrated 3D sequential technology. An example of a 3D integration is shown in Fig. 1 through a two level CMOS inverter.

Figure 1: Cross-sectional TEM image of 3D inverter made of a bottom level NMOS and a top level PMOS

The objectives of this work were twofold (1) to address how the top level processing impacts the performance and reliability of the bottom one (2) to assess the intrinsic reliability of the top level device processed at 630°C; a much lower temperature than for

a conventional gate first integration process T>1000°C. To investigate (1), we compared the BTI reliability of bottom level transistors, which have seen the process of the top level, to the one of simple planar 2D references (only ground level, no level on the top). For BTI (see Fig.2) as well as for Hot Carrier (not shown here), no difference is visible between both kinds of devices. This clearly demonstrates that the gate oxide quality of the bottom level devices is not altered by the top level processing at 630°C. For (2), we compared the BTI lifetime of Bottom and Top level NMOS and PMOS devices (see Fig. 3). Even if PBTI is slightly degraded for top level devices, the BTI requirements -VG for 5 years working must be over 0.95V - are met for both bottom and top transistors. This is a first demonstration that 3D sequential technology can reach the reliability standards for digital CMOS applications [2].

Figure 2: Impact of top level processing on BTI reliability the bottom level transistor.

Figure 3: Extraction of BTI lifetime for bottom and top leve transistors. BTI lifetime Is over 5 vears in all cases · (>V<sub>DD</sub>+5%=0.95V)

#### **Perspectives**

The key challenge will be now to reduce the temperature of the top level process below 600°C while keeping the same quality of the top transistor gate oxide. This is required to cope with all the possible applications targeted by this technology.

- [1] L. Brunet et al., Electrochemical society spring meeting, Seattle, 2018, 10.1149/08508.0125ecst [2] A. Tsiara et al., Proceedings of IEEE Symposium on VLSI Technology, 2018, 10.1109/VLSIT.2018.8510625

# Low Temperature Epitaxy and Clean for CoolCube™ Integration

#### **RESEARCH TOPIC:**

Low temperature Si and SiGe selective epitaxy, Siconi surface preparation, CoolCube<sup>™</sup> integration

#### **AUTHORS:**

V. Mazzocchi, P.E. Raynal, V. Loup and J.M. Hartmann (P. Besson, J.B. Pin)

#### **ABSTRACT:**

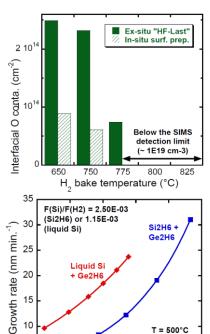

The features of Metal Oxide Semiconductors Field Effect Transistors (MOSFETs) become smaller and smaller in advanced technology nodes, with a clear switch from planar to 3D devices such as finFETs or stacked nanosheets. Monolithic 3D integration, i.e. Coolcube<sup>TM</sup>, is definitely an option in order to increase the density of devices per footprint. It consists in stacking layers of transistors on top of one another, with definite constraints concerning the thermal budget used for top device fabrication (it should be low in order not to degrade the performances of the bottom devices). We are evaluating various strategies in order to minimize the temperature used during (i) surface preparations and (ii) epitaxial growth processes, which should be selective against dielectrics, 500°C being the targeted value.

INDUSTRIAL COLLABORATIONS: AMAT, STMicroelectronics

#### **Context and Challenges**

Low temperature selective epitaxy is of paramount importance in order to (i) thicken the Source and Drain regions of top level Metal Oxide Semiconductor Field Effect Transistors without degrading the properties of bottom MOSFETs (in monolithic 3D integration), (ii) encapsulate small 3D objects such as fins without altering their shape and so on.

Such processes consist in a surface preparation (made of a wet cleaning, potentially an in-situ NH<sub>3</sub>/NF<sub>3</sub> remote plasma Siconi<sup>TM</sup> process and an in-situ H2 bake) followed by the growth itself, which can occur in a single step (with chlorinated gaseous precursors, usually) or through an alternating between nonselective growth steps (with hydrogenated precursors) and selective etch steps (with HCl or Cl<sub>2</sub>). In the following, we will show some of the results we have obtained on (i) the impact of a Siconi™ process on the surface preparation of Si and SiGe and (ii) the low temperature growth kinetics of Si and SiGe with mixtures of conventional gaseous precursors or liquid Si.

#### Main Results

We have evaluated in Ref. [1] the interest of using an in-situ Siconi™ process, which transforms native or chemical oxides into salts which can be sublimated at low temperatures, avoiding thereby surface re-oxidation during wafer transfer. On Si surfaces, we succeeded in reducing by 25°C the threshold H<sub>2</sub> bake temperature above which there are no interfacial oxygen peaks anymore (see Fig. 1 (top)). We otherwise obtained much lower O interfacial contamination at temperatures less than 750°C, which has an impact on epitaxial quality. We also showed that ex-situ wet cleanings creating SiO2-rich chemical oxides followed by Siconi™ processes yielded smooth SiGe surfaces free of any oxide.

We have investigated in Ref. [2] the impact Si precursor mixing has on the Si and SiGe growth kinetics in the 500°C-575°C range, with far from straightforward trends observed. We have otherwise benchmarked, for the same purpose, a liquid Si precursor against disilane. Significantly higher growth rates for a given Ge concentration were obtained with the former at 500°C, as shown in Fig. 1 (bottom). Reasonable Si growth rates were achieved with liquid Si at temperatures as low as 475°C, i.e. 75°C lower than with silane (SiH<sub>4</sub>), for instance.

#### **Perspectives**

The fitness of the sequence proposed for SiGe surface preparation is being evaluated through the re-epitaxy of SiGe on top, with interesting trends emerging. Liquid Si is being used in non-selective growth steps together with Cl2 selective etch steps to fabricate Si raised sources and drains at 500°C.

Figure 1: (top) interfacial O contamination (in Si) as a function of the H₂ bake temperature after "HF-Last" or Siconi™ surface preparations (bottom) Growth rate versus Ge concentration for different chemistries, showing the interest of using liquid Si.

35

T = 500°C

P = 20 Torr

45

40

Ge concentration (%)

10

#### RELATED PUBLICATIONS:

[1] J.M. Hartmann et al., ECS Transactions 86 (7) 219, 2018, 10.1149/08607.0219ecst [2] V. Mazzocchi et al., ECS Transactions, 86 (7) 177, 2018, 10,1149/08607,0177ecst

# **Advanced FDSOI CMOS: Strain Optimization and Design Technology co-Optimization**

#### **RESEARCH TOPIC:**

FDSOI, DTCO, strain, Body biasing, Local Layout Effect

#### **AUTHORS:**

F. Andrieu, C. Fenouillet-Beranger, O. Weber, M. Vinet, R. Berthelon, D. Rouchon, G. Cibrario, B. Giraud

#### **ABSTRACT:**

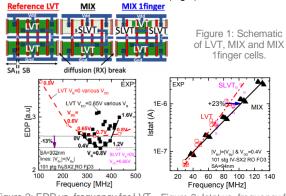

Performance/Power/Area of CMOS digital circuits on next-node FDSOI can be improved by strain optimization and Design/Technology Co-Optimization (DTCO). LETI has carried out studies to measure the strain by Raman for different CMOS process integration schemes in order to optimize the performance. Moreover, DTCO was carried out in SRAM leading to an innovative Complementary SRAM design using SiGe channel in the pass-gate. Finally, for standard cells, we propose an original Technology/Design Co-optimization, mixing devices of different threshold voltages (V<sub>T</sub>-flavors) within a cell. It enables adjusting the V<sub>T</sub> of pMOS subject to SiGe channel-induced Local Layout Effect (LLE); leading experimentally to a 23% frequency gain on 22nm FDSOI technology for a 2-finger inverter Ring Oscillator (IVSX2 RO) vs. reference LVT at the same static leakage and V<sub>DD</sub>=0.4V supply voltage; which corresponds to the Minimum Energy Point (MEP). This solution is combined with Forward Body Biasing (FBB). SCIENTIFIC COLLABORATIONS: STMicroelectronics (France), Globalfoundries (Dresden, Germany)

#### **Context and Challenges**

FDSOI CMOS offers an excellent performance/power/cost tradeoff for mobile, IoT and wearable applications. Moreover, its excellent electrostatic control and variability, as well as its backbias capability, make it a good candidate for Ultra-Low-Voltage (ULV) operations. Performance/Power/Area tradeoff can be optimized for next FDSOI by strain optimization and Design/Technology Co-Optimization (DTCO).

#### Strain optimization

We fabricated SiGeOI by the Ge-enrichment process and SiGe/SOI bilayer by epitaxy. On these materials, nanosheets were patterned down to 100 nm width and characterized by µRaman spectroscopy for different CMOS process integration schemes. We evidence experimentally a relaxation of the compressive strain in SiGe for narrow lines, which is higher for SiGeOI than for SiGe/SOI at W=500 nm, in qualitative agreement with the electrical results we measured on planar FDSOI pMOSFETs. We highlight the interest of a tensile nitride capping on top of SiGe in order to maintain the stress during active patterning and demonstrate that a 0.45% tensile stress could be generated in 100 nm narrow stripes in the underneath SOI layer of the SiGe/SOI bilayer [1].

#### DTCO in SRAM

We investigated the introduction of an SiGe channel in FDSOI SRAM bitcells by the means of spice simulation. In classical SRAM configuration performance (read, write, retention) at a given leakage is only slightly impacted because of the SiGe stress partial relaxation in the small Pull-Up active dimensions. Since the SiGe compressive stress strongly enhances the hole mobility for long active stripes, it is relevant to design a so-called Complementary-SRAM bitcell, using SiGe pFETs as both Pull-Up and Pass-Gate devices. In such an innovative configuration, the read current is enhanced by +21% with respect to the reference at the same leakage.

#### **DTCO** in standard cells

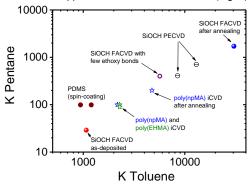

Local Layout Effect (LLE) induced by SiGe-channel impacts the device centering in advanced FDSOI technologies. Process or (continuous-RX) design solutions exist to suppress LLE and get the maximum performance from the SiGe booster. We have proposed an original design that mitigates SiGe-induced LLE to increase the performance while preserving low-leakages. It consists in mixing within a standard cell different  $V_{\mathsf{T}}$  flavors (Fig.1). Some 22FD-SOI ULV features were measured on inverter ROs: Minimum Energy Point (MEP) below 0.4 V and min Energy-Delay-Product (EDP) at V<sub>DD</sub>≈0.65 V for LVT. We show also for the first time that an optimum V<sub>B</sub> exists leading to -13% min EDP (vs. V<sub>B</sub>=0) (Fig.2). On these ULV cells using within-cell  $V_T$ -mixing, leads to +23% frequency for IVSX2 vs. ref LVT at the same static leakage and V<sub>DD</sub>=0.4 V (Fig.3).

Figure 2: EDP vs. frequency for LVT V<sub>B</sub>=0 (various V<sub>DD</sub>) and at V<sub>DD</sub>=0.65V (various  $V_B$ ). Lines correspond to  $|V_{Bn}| = |V_{Bp}|$

Figure 3: Istat vs. frequency for LVT, SLVT and MIX

#### **Perspectives**

FDSOI is an attractive technology for IoT, edge-IA, RF applications. 28 nm, 22 nm and 12 nm CMOS platforms exist in the industry and solutions for sub-12 nm have been developed at LETI.

- [1] R. Berthelon et al., SSDM, 2018; <a href="https://confit.atlas.jp/quide/event/ssdm2018/subject/C-3-02/date?cryptold=">https://confit.atlas.jp/quide/event/ssdm2018/subject/C-3-02/date?cryptold=</a>

[2] F. Andrieu et al., IEEE VLSI Symposium, 2018, <a href="https://doi.org/10.1109/VLSIT.2018.8510636">10.1109/VLSIT.2018.8510636</a>

[3] R. Berthelon et al., EuroSOI, 2018, <a href="https://doi.org/10.1109/VLSIS.2018.8354730">10.1109/VLSIS.2018.8354730</a>

## Recent Bulk Modelling Development on **PSP Model and Prospective Modeling of Single Event Transients.**

#### **RESEARCH TOPIC:**

PSP, Single Event Transients, Compact model, SPICE, Bulk transistor

#### **AUTHORS:**

S. Martinie, O. Rozeau, N. Rostand, J. Lacord, T. Poiroux, J-C. Barbé (André Juge, Geert D. J. Smit, G. Hubert)

#### **ABSTRACT:**

With the maturity of CMOS technologies and their use for low voltage analog applications, some additional parasitic effects must be modeled to improve the accuracy of SPICE models. This paper describes the latest significant improvements of PSP bulk MOSFET model including new compact models of parasitic MOSFET and interface states. We also presented our recent work on Single Event Transients (SET) which are important issues concerning reliability. They lead to occurrence of soft errors in integrated circuits, such as Single Event Upset (SEU), which consists in unexpected bit state switch in SRAM cells. Here, we describe the implementation in Verilog-A of a new approach and use it to study the effect of SET on SRAM cell.

SCIENTIFIC COLLABORATIONS: STMicroelectronics, NXP Semiconductors, ONERA.

#### **Context and Challenges**

PSP is a standard compact model for deep-submicron bulk Metal-Oxide-Semiconductor Field Effect **Transistors** (MOSFETs). Since 2015, CEA-LETI is the main developer of PSP and continues to improve accuracy in-line with industrial expectations. Especially, with the decrease of supply voltage, devices operate close to the weak inversion, where some effects such as parasitic sidewall transistor, and the interface states effect, can have a significant impact. On the other hand, the effect of natural radiations (neutrons ...) on CMOS circuits has been widely demonstrated and are even more significant as we decrease transistor sizes. SET are one of these effects and consist in the formation of parasitic current pulses within MOSFETs after the particle impact. Here, we explore new ways of modeling development to include the SET effect into the compact model formalism.

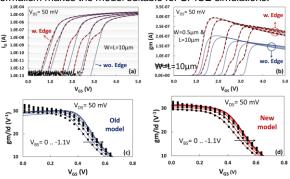

#### Main Results

Fig. 1.a & b represents different figures of merit on current and gm versus gate voltage for different values of back gate voltage and two geometries (large W=L=10 μm and narrow W=0.5 μm L=10 µm transistor). The hump induced by the parasitic transistor is well reproduced by the proposed model even for narrow transistors, where the parasitic transistor is predominant on total current as highlighted on gm of figure 1.b.

The influence of non-uniform related DIT parameter is relatively slight on IV curve. On the other hand on gm/ld (which is one of the key figures of merit in analog design), in figure 1.c & d, we observe clearly the improvement by using a new model of nonuniform DIT particularly evident on gm/ID curves.

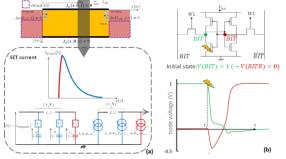

The proposed model for SET has been implement in a Verilog-A code that is based on a finite number of RC circuits (cf figure 2.a). The input of the model are particle parameters, the ambipolar diffusivity and the splitting width. Finally, such a formalism makes the SET model suitable for SPICE circuit simulations and we showed some useful SPICE applications (cf figure 2.b).

#### **Perspectives**

For PSP we continue our effort to improve accuracy in accordance with industrial expectation. For SET, such a formalism makes the model suitable for SPICE simulations.

Figure 1: Comparison between experiments (dotted line) and model (red line with and blue line without new model) for linear current (ID) (a), first derivative (gm) (b), gm/ld versus without (c) and with (d).

Figure 2: (a) Illustration of physical system with the SET current pulse with the equivalent circuit model proposed. (b) SPICE simulation of SEU occurrence in a SRAM cell using our model.

- [1] S. Martinie et al., SISPAD, 2018, DOI: <u>10.1109/SISPAD.2018.8551712</u> [2] N. Rostand et al., SISPAD, 2018, DOI: <u>10.1109/SISPAD.2018.8551633</u>

## Strain Maps And Tunability of Parasitic Channel in Gate-All-Around Stacked Nanosheets FETs

#### **RESEARCH TOPIC:**

MOSFET, gate-all-around nanosheet, 5 nm node and beyond, replacement-metal-gate-process, SPICE, NSP model.

#### **AUTHORS:**

S. Barraud, S. Reboh, B. Previtali, V. Lapras, R. Coquand, J.-M. Hartmann, S. Martinie, N. Bernier (M-P. Samson, N. Loubet).

#### **ABSTRACT:**

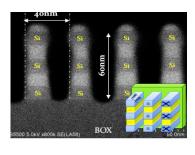

A comprehensive study going from the integration of 3D stacked nanosheets Gate-All-Around (GAA) MOSFET devices to SPICE modeling is proposed. Devices are fabricated on SOI substrates using a replacement high- $\kappa$  metal gate (RMG) process and self-aligned-contacts. Strain, stress, and mechanical relaxation in fin-patterned Si/SiGe multilayers are investigated. Back-biasing is also efficiently used to highlight a drastic improvement of electrostatics in the upper GAA Si channels. Advanced electrical characterization of these devices enabled us to calibrate a new version of physical compact model (NSP) in order to assess the performance of ring oscillators for different configurations of GAA FETs integrating up to 8 vertically stacked Si channels.

SCIENTIFIC COLLABORATIONS: STMicroelectronics (France), IBM research (USA).

#### **Context and Challenges**

After being proposed and developed a little more than ten years ago, stacked nanosheets (NS) gate-all-around (GAA) MOSFETs are becoming an industrial reality. After FinFET, GAA multichannels are a new class of advanced CMOS delivering higher performances, consuming less and pushing further scaling limits. Research conducted over the last three years has allowed to make major advances to now place this novel technology in the roadmap of leading chipmakers.

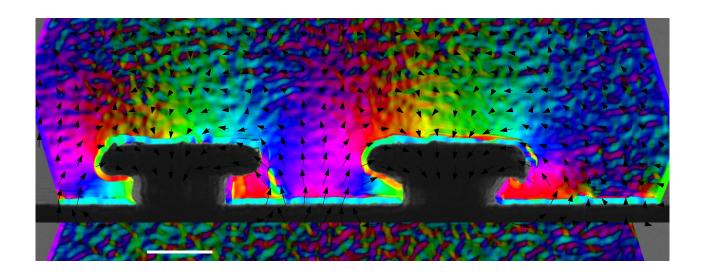

#### **Main Results**

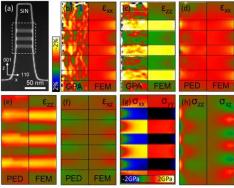

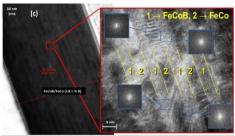

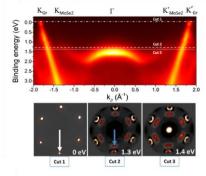

In this work, advanced transmission electron microscopy is used to investigate strain and stress relaxation effects in fin-shaped structures of (Si/SiGe) multilayers. With experimentally validated numerical models based on a finite element method (FEM), we provided quantitative descriptions of strain and stresses in the structures [1] as shown in fig. 1.

Figure 1: Cross-sectional dark-field STEM micrograph of Si/SiGe multilayers. Strain maps obtained by GPA for (b)  $_{\text{EXX}}$  and (c)  $_{\text{EZZ}}$  and by PED for (d)  $_{\text{EXX}}$ , and (e)  $_{\text{EZZ}}$ , and (f)  $_{\text{EZX}}$ . Calculated strain (FEM) are shown in the right side of the Images.

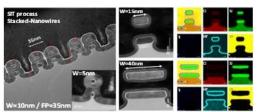

Figure 2: TEM images of (SiGe/Si) fins obtained by SIT which have a fin pitch of 35nm and a W=10nm width. A wide range of W is considered.

Then, GAA stacked-NS FETs (Fig. 2) are fabricated with a RMG process and self-aligned contacts. The impact of size (W, gate length) and substrate orientation on electrostatics and the overall performance of stacked wires n-FETs is studied. A good electrostatic control is shown despite lower trigate Si channel (DIBL=80mV/V at L<sub>G</sub>=20nm). Next, back-biasing was used to tune the threshold voltage of the lower trigate Si channel and focus on the electrostatics properties and transport in the upper GAA Si channel. Effectiveness of reverse back-biasing channel modulation resulted in a drastic improvement of electrostatic properties in GAA structures. This can be considered as an additional lever to offer more power/perf. flexibility in 3D stacked channels. Finally, NSP compact model has been validated with experimental data on large ranges of applied biases and device geometries. The good agreement with experiment demonstrated the accuracy of our physical compact model to predict GAA stacked-NS operation. Then, based on this model, SPICE modeling allowed the assessment of ring oscillator performance for different configurations of GAA FETs integrating up to 8 vertically stacked Si channels [2].

#### **Perspectives**

Further developments to increase the drive current per layout footprint and the predictability of compact modeling for stackednanosheet devices are in progress.

- [1] S. Reboh et al., Appl. Phys. Lett. 112, 051901 (2018); DOI: 10.1063/1.5010997

- [2] S. Barraud et al., in IEDM Technical Digest, pp. 21.3.1-21.3.4 (2018); DOI: 10.1109/IEDM.2018.8614507

02

# **MEMORIES**

- OTS Selectors for Emerging Memories

- Resistive Memories for Spiking Neuromorphic Circuits

- Next Generation of Phase-Change Memory: Performances Challenges Enabled by Scientific and Technology Innovation

- RRAM Reliability Improvement

# **OTS Selectors for Emerging Memories**

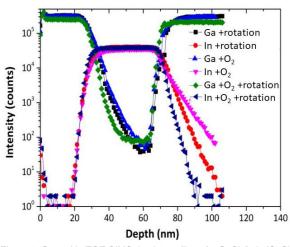

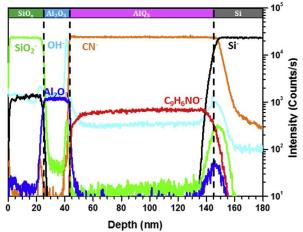

#### **RESEARCH TOPIC:**

Backend Selector, Ovonic Threshold Switching (OTS)

#### **AUTHORS:**

A. Verdy, M. Bernard, G. Bourgeois, P. Noé, J. Garrione, M. C. Cyrille G. Navarro and E. Nowak

#### **ABSTRACT:**

Back-End selector technology is fundamental for the implementation of high-density 3D Resistive Crossbar Arrays. Among the several Back-End selector devices developed in the last years, Ovonic Threshold Switching selector (OTS) represents a promising candidate. The development of OTS devices requires material as well as device engineering. At LETI, both these activities are ongoing in order to achieve highly reliable and BEOL-compatible selector devices. Our investigations highlight the OTS and the memory parameters that can influence the functionality of a crossbar array, in particular during the reading operations. High temperature reliability, high endurance and low leakage current achieved in our OTS devices represent key achievements towards reliable and high-density crossbar based architectures.

**SCIENTIFIC COLLABORATIONS: STMicroelectronics**

#### **Context and Challenges**

Resistive Crossbar Array (RCA) represents the most suitable technological solution as Storage Class Memory (SCM) to overcome the actual memory architecture bottleneck represented by the huge latency difference between the main memory (DRAM) and the storage (Flash Memory). Moreover, it opens the way for new paradigms for non-Von Neumann architectures such as neuromorphic accelerators or in-memory computing. RCA requires the integration in the Back-End-of-Line (BEOL) of the fabrication, making essential for its functionality a BEOL access selector device, such as the Ovonic Threshold Switching selector (OTS). The OTS engineering and reliability becomes fundamental to achieve high RCA performances.

#### **Main Results**

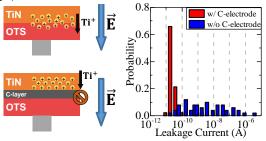

In order to push the OTS selector performances, we analyzed the interaction of the material with the surrounding electrodes. We highlighted the important diffusion of the metallic electrode inside the OTS material that occurs during the operations of the device, resulting in an important increased and dispersed leakage current. Inserting a thin carbon layer as diffusion barrier results in an ultra-low leakage current and improved reliability (Fig.1).

Figure 1: Carbon layer is used as diffusion barrier, enabling ultra-low leakage current and improved reliability of the devices

Figure 2: Material engineering in Ge-Se-Sb-N system permits to achieve devices featuring low leakage current, low operating voltage (a), BEOL thermal budget compatibility and high endurance (b). Simulations of the reading window and of the array size as a function of the operating temperature for an RCA integrating our optimized OTS selector (c).

We show that in the Ge-Se-Sb-N system, low operating voltage, low leakage current, BEOL compatibility and high endurance (Fig. 2a, b) are achieved thanks to proper doping and a specific thermal annealing procedure responsible for a beneficial material reorganization.

Investigations on the read operation highlighted the need for reliable measurements of new metrics, such as the OTS threshold current, and for the evaluation of the influence of the operating temperature on the OTS and on the memory parameters. We clearly showed how the final performance of the RCA depends on such parameters (Fig. 2c).

#### **Perspectives**

This work paves the way for further developments, targeting large crossbar arrays for SCM and neuromorphic applications. It enables design rules in order to optimize the OTS selector to fulfill the specifications required for the co-integration with different resistive memories (such as PCRAM, OxRAM or CBRAM).

- [1] A. Verdy et al., IEEE International Electron Devices Meeting (IEDM), 2018, San Francisco, CA, USA, DOI: 10.1109/IEDM.2018.8614686

- [2] A. Verdy et al., 2018 IEEE International Memory Workshop (IMW), Kyoto, Japan, DOI: 10.1109/IMW.2018.8388834

[3] A. Verdy et al., 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, DOI: 10.1109/IRPS.2018.8353635

# **Resistive Memories for Spiking Neuromorphic Circuits**

#### **RESEARCH TOPIC:**

RRAM, TCAM, neuromorphic circuits, characterization, reliability, performance, artificial synapses

#### **AUTHORS:**

E. Vianello, D. R. B. Ly, J.-P. Noel, B. Giraud, A. Grossi, A. Valentian, E. Nowak (D. Querlioz), (G. Indiveri)

#### **ABSTRACT:**

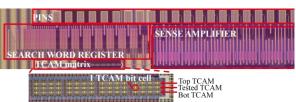

Resistive Memory (RRAM) technology can play a crucial role for the design of neuromorphic circuits. First, RRAMs can be used to reproduce artificial synapses. We demonstrated that a neural network that learns through the Spike Time Dependent Plasticity algorithm (an on-line and unsupervised algorithm) not only holds up well against RRAM non-ideality, but they can draw benefits from it. Second, RRAMs can play a crucial role in the design of asynchronous routing for implementing scalable multi-core neuromorphic architectures. We demonstrated that RRAM-based ternary-content addressable memory (TCAM) circuits meet the performance and reliability requirements of multicore neuromorphic processors.

SCIENTIFIC COLLABORATIONS: Univ. Paris-Sud, University of Zurich and ETH Zurich

#### **Context and Challenges**

Resistive switching memories (RRAMs) represent a promising technology for building neuromorphic circuits. First, they have attracted wide interest as adaptive synaptic elements in artificial bio-inspired Spiking Neural Networks (SNNs). Second, we have recently proposed RRAM-based ternary-content addressable memory (TCAM) circuits for the design of asynchronous routing in multicore neuromorphic processors

#### **Main Results**

First, we investigated the role of RRAM non-idealities (resistance variability, number of resistance levels) in Spiking Neural Networks (SNNs) based on RRAM synapses. We analyzed the role of synaptic (RRAM) non-idealities during on-line unsupervised learning by Spike-Timing Dependent Plasticity (STDP) for detection in dynamic input data and classification of static input data. We demonstrated that SNNs are not only robust to synaptic variability, but can also draw benefit from it. RRAM variability can be beneficial as it increases the range of synaptic weight values available during learning. For detection applications, binary RRAM technology is well-suited to implement synaptic elements as only one RRAM device per synapse is needed. On the other hand, for classification applications, multilevel conductance synapses are necessary to achieve the best performance; a synaptic compound composed of at least 10 OxRAMs per synapse is required.

Second, we fabricated and fully characterized a RRAM-based ternary-content addressable memory (TCAM) circuit. TCAM circuits allow searching for stored information by its content, as opposed to classic memory systems in which a memory cell's stored information is retrieved by its physical address. They shorten the search time compared to classic memory-based search algorithms, as all the stored information is compared with the searched data in parallel, within a single clock cycle. However, conventional SRAM-based TCAM circuits are usually implemented with 16 CMOS transistors, which limits storage capacity of TCAMs to tens of Mbs in standard memory

structures, and takes up valuable silicon real estate in neuromorphic computing spiking neural-network chips. The fabricated RRAM-based TCAM circuit replaced SRAM cells with RRAM to reduce the number of required transistors to two (2T), and to two RRAMs (2R), which is the most compact structure for these circuits produced to date. In addition, the RRAMs were fabricated on top of the transistors, which also consumed less area. This suggests such a 2T2R structure can decrease the required TCAM area by a factor of eight compared to the conventional 16-transistor TCAM structure. However, while using RRAMs in TCAM circuits significantly reduces both silicon chip area needed and power consumption, this approach brings new challenges: first, the size of the TCAM memory is limited by the ratio between the ON and OFF states of the RRAM cells (~10-100). Second, RRAMs have a limited endurance with respect to CMOS transistors, which can affect the lifespan of the system. The TCAM cells used in multicore neuromorphic processors are typically small in size and are programmed only at network configuration time, thus they perfectly meet the performance and reliability of the proposed circuit.

Fig. 1 Fabricated and tested RRAM-based TCAM circuit.

### **Perspectives**

These results give some guidelines to design SNNs based on RRAM to implement both synapses and routing.

<sup>[1]</sup> D.R.B. Ly et al., IEEE International Electron Devices Meeting (IEDM), 2018, San Francisco, CA, USA, DOI: 10.1109/IEDM.2018.8614603

<sup>[2]</sup> D.R.B. Ly et al., J. Phys. D: Appl. Phys. 51, 2018, https://iopscience.iop.org/article/10.1088/1361-6463/aad954/meta

[3] A. Grossi et al., ,IEEE Transactions on Very Large Scale Integration (VLSI) Systems. Vol. 26, NO. 12, Dec. 2018;: 10.1109/TVLSI.2018.2805470

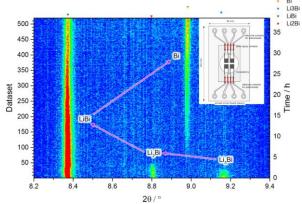

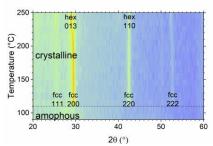

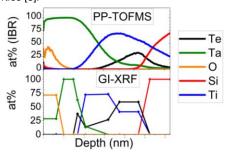

# Next Generation of Phase-Change Memory: Performances Challenges Enabled by Scientific and Technology Innovation

#### **RESEARCH TOPIC:**

Non-volatile Resistive Memory, Phase-Change Memory (PCM), chalcogenides, Storage Class Memory (SCM)

#### **AUTHORS:**

G. Bourgeois, A. L. Serra, M. C. Cyrille, J. Garrione, C. Sabbione, V. Beugin, N. Castellani, J. Sandirini, G. Navarro, E. Nowak, (C. Vallée)

#### **ABSTRACT:**

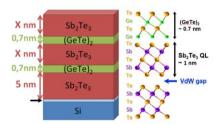

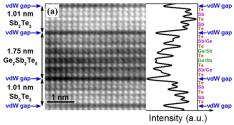

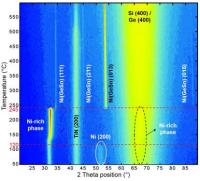

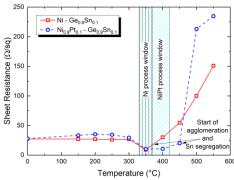

We propose different ways of engineering the Phase-Change Memory device targeting a highly energy efficient cell. We show that electrical and thermal confinement improvement of the phase-change material enables a high reduction of the programming current, achieved also by the optimization of the device architecture, in particular in the case of a confined structure. Furthermore, we demonstrate the reduction of thermal losses by the tuning of the thermal conductivity of the dielectrics surrounding the phase-change material. Finally, we propose some considerations about material engineering, as demonstrated in SLL-PCM (superlattice like PCM) whose thermal properties could lead to significantly improved efficiency of the cell.

**SCIENTIFIC COLLABORATIONS:**

CNRS-LTM, STMicroelectronics

#### **Context and Challenges**

Phase-Change Memory (PCM) is today the most mature among innovative back-end non-volatile memory technologies (NVM). Its recent commercialization to address stand-alone Storage Class Memory (SCM) applications demonstrates its advanced state in terms of industrialization. Moreover, PCM technology is versatile enough to meet different applications' requirements and recent progress in material engineering opens new ways to target both data retention and programming speed. Thus, charge based Flash memory will be highly challenged by PCM at the low power portable applications age, making the cell efficiency a must for next generation of NVM.

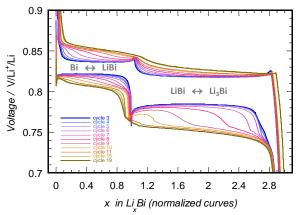

#### **Main Results**

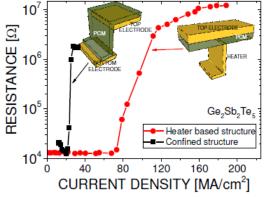

The PCM « confined structure » allows a six-fold reduction of the current density with respect to a heater based structure, thanks to a drastic material volume and thermal confinement. This cell structure optimization forces the localization of the amorphous region along the sidewall of the structure, creating an active region fully amorphized at once which explains the abrupt transition between the SET and the RESET state (Fig. 1).

Figure 1: Programming characteristics for a standard PCM device (heater based) and an optimized Confined structure.

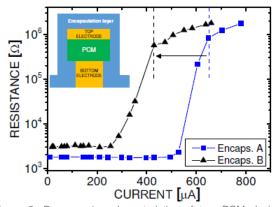

Figure 2: Programming characteristics of two PCM devices integrating two different encapsulation layers.

A further reduction of the programming power can be achieved thanks to the engineering of the dielectrics that surround the device. The lower thermal conductivity of layer B with respect to layer A, preventing heat losses, allows a RESET operation at lower current (~ 30% of reduction) (Fig. 2). We also investigated a standard PCM lance-type cell integrating an optimized  $GeS_2/Sb_2Te_3$  material obtained by co-sputtering, leading to both an electrical (i.e lower volume) and a thermal confinement improvement (i.e a higher power efficiency). Indeed,  $Sb_2Te_3$  nanocrystals formation in  $GeS_2$  amorphous matrix, so called GSST based PCM cell, leads to a great reduction of the programming current (more than ten times) compared to standard  $Ge_2Sb_2Te_5$ .

#### **Perspectives**

Beyond PCM device engineering, new thermal properties can be involved in multilayers phase-change films, in particular phonon scattering at interfaces creating a huge thermal confinement along the z-axis of the cell. These developments reveal the possibility to engineer and target high-energy efficient next generation PCM, for low power/high density memory applications.

- [1] G. Navarro et al., IEEE International Memory Workshop (IMW), 2018, Kyoto, Japan, DOI: 10.1109/IMW.2018.8388845

- [1] G. Navano et al., IEEE litternational Memory Workshop (MWW), 2016, Ryoto, Japan, BOL. 10.1109/MWV.2018.0506045 [2] G. Bourgeois et al., Non-Volatile Memory Technology Symposium (NVMTS), 2018, Sendai, Japan , http://www.cies.tohoku.ac.jp/nvmts2018/program/day\_2.html

# **RRAM Reliability Improvement**

#### **RESEARCH TOPIC:**

Resistive Memory, Non Volatile Memory, reliability

#### **AUTHORS:**

G. Sassine, D. Alfaro Robayo, J.-F. Nodin, J. Coignus, C. Cagli, E. Nowak, G. Molas, (Q. Rafhay, G. Ghibaudo)

#### **ABSTRACT:**

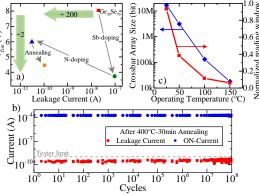

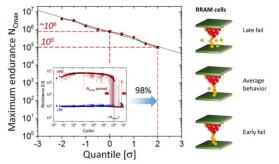

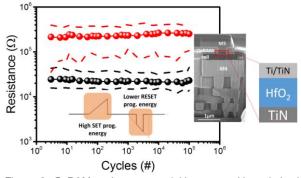

We deeply investigated RRAM endurance at the statistical level. Understanding of RRAM endurance fail is analyzed experimentally on 4 kb memory arrays and theoretically thanks to numerical simulations. Then, reliability improvement is achieved by optimizing programming energy on RRAM 1T1R kb arrays. SET and RESET programming patterns are optimized with programming current of 50 µA, to minimize the energy provided to the system, maintaining sufficient widow margin on resistance distribution tails. Maximum endurance was improved of about 2 cycling decades up to 107 cycles, error tails were significantly reduced even for programming currents of 50 µA, required for low power applications.

SCIENTIFIC COLLABORATIONS: IMEP LAHC CNRS (Grenoble, France)

#### **Context and Challenges**

RRAM variability is today the main roadblock to be solved before mass production could be envisaged. In this context, reliability improvement has to be addressed by analysis at the statistical level, studying RRAM arrays. In this work, we analyze RRAM endurance failure at the statistical level and propose a model to perform predictive extrapolations [1]. We optimize SET RESET patterns by adjusting programming energy, resulting in significant endurance and retention improvement [2]. Finally, we significantly reduce RRAM programming consumption of slow tails in memory populations [3].

#### **Main Results**

Results were obtained on RRAM technologies integrated in our 200 mm test vehicle. Both HfO2/Ti OXRAM and Al2O3/CuTex CBRAM were investigated.

We demonstrated that RRAM maximum number of cycles (endurance) follows a log normal distribution law (Fig.1). Endurance dispersion depends on RRAM stack (materials and thicknesses). Adjusting RESET voltage allows to optimize endurance statistics and reduces cycling performances dispersion.

Figure 1: RRAM (Al<sub>2</sub>O<sub>3</sub>/CuTe<sub>x</sub>) maximum endurance distribution measured on 4kb arrays.

Figure 2: OxRAM endurance on 4 kb arrays with optimized patterns showing no overlap of ON (black) and OFF (red) resistances (dashed lines: 95% of the cells).

RRAM endurance evaluation at the array level is therefore mandatory to confront RRAM device reliability with industrial requirements before technology ramp up could be envisaged. Then we improve RRAM endurance by optimizing programming energy on HfO<sub>2</sub>/Ti OXRAM kb arrays. Optimized ramp voltage based programming scheme minimizes the energy provided to the system RESET. It allows to improve maximum endurance by about 2 decades, to insure stable median window margin at 107 cycles and to maintain window margin at 2<sub>o</sub> after 10<sup>6</sup> cycles at 50 µA for low power applications.

#### **Perspectives**

Significant improvement of RRAM reliability (endurance, retention, consumption) was proposed, optimizing programming scheme, thanks to the understanding of the device at the microscopic level. Next step will consist in the co-integration of a back-end OTS selector with the memory and analysis of impact of RRAM variability on the device performances.

- [1] D. Alfaro Robayo et al., 2018 Int. Symp. on VLSI Tech., Systems and Application (VLSI-TSA), Hsinchu, Taiwan, DOI: 10.1109/VLSI-TSA.2018.8403856 [2] G. Sassine et al., 2018 IEEE International Memory Workshop (IMW), Kyoto, Japan, DOI: 10.1109/IMW.2018.8388843 [3] G. Sassine et al., IEEE Journal of the Electron Device Society, 6, (2018), DOI: 10.1109/JEDS.2018.2830999

03

# **PATTERNING**

- Innovative Etching Approach for Low-k Spacer Patterning

- Fine-Tuning of Surface Energies for DSA Patterning

- Pushing Line Roughness Metrology Techniques to their Limits

- Lithography Computational Aspects for Mask Writing

- Advanced Design Correction for Wafer Scale NanoImprint Process

- Multibeam Lithography: Process Integration Flow and Associated Metrology

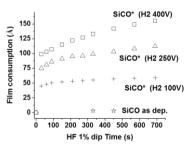

# Innovative Etching Approach for Low-k Spacer Patterning

#### **RESEARCH TOPIC:**

Thin layer etching, Low-k, spacer fabrication, SiCO, FDSOI

#### **AUTHORS:**

N. Posseme, O. Pollet, (M. Garcia Barros), (F. Leverd), S.Barnola

#### **ABSTRACT:**

Low-k spacer etching realization is considered today as one of the most challenging processes for the manufacturing of fully depleted silicon on insulator devices. Indeed, such films, required to replace conventional silicon nitride to improve device performances, leads to critical patterning issues due to its high sensitivity to fluorocarbon based plasma. To overcome these issues and meet the stringent etch requirements of traditional spacer realization (no foot formation, critical dimension control below one nanometer), a new process was developed to etch SiCO Low-k spacer.

**SCIENTIFIC COLLABORATIONS: STMicroelectronics**

#### **Context and Challenges**

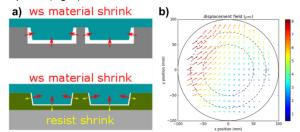

Spacer etching is still challenging for the production of high performance Fully Depleted Silicon On Insulator (FDSOI) device production. A trade-off has to be found between silicon germanium (or silicon) recess, foot formation and spacer faceting on top of the hard mask directly impacting the device performances. This challenge is all the more critical for the introduction of low-k film instead of traditional silicon nitride. Indeed, such low-k films are more sensitive to fluorocarbonbased chemistries, leading to critical patterning issues. To overcome these issues, we proposed a new etch approach for silicon oxycarbide (SiCO) [1] concerns. The new etching process is based on two steps. The film is firstly modified by a H<sub>2</sub> plasma (labeled as SiCO\*) performed in an Inductively-Coupled (ICP) Plasma chamber followed in a second step by a 1% HF wet cleaning to remove the modified layer selectively to the nonmodified materials (SiCO, Si or SiGe).

#### **Main Results**

A precise control of the SiCO\* film damage thickness, can be tuned using the plasma operating conditions such as bias voltage or process time (Fig.1).

Figure 1: Evolution of the SiCO\* film consumption as a function of bias voltage and HF dip time.

Infrared spectroscopy analyses revealed that the  $H_2$  plasma exposure leads to SiCO film oxidation with important Si-H and silanol group formation. This carbon depletion confirmed by XPS after  $H_2$  plasma (converting the SiCO film into SiOxHy film) is responsible at the first order for the higher etch rate when SiCO\* is dipped in liquid phase HF.

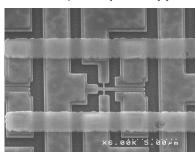

Application on patterns showed that this approach offers an interesting alternative to conventional fluorocarbon based chemistries. Indeed, after  $H_2$  plasma followed HF dip, the SiCO spacer can be etched without underneath film modification, no foot formation and less than 2 nm lateral consumption (Fig.2).

Fig 2: TEM image of a 14 nm FDSOI transistor gate. SiCO spacer etching was performed by H<sub>2</sub> plasma implantation followed by 1% HF dip followed by SiGe epitaxial growth.

A consumption of the  $SiO_2$  hard mask (not compatible with long HF dip time) is also observed in Fig. 2, explaining the EPI regrowth on top of the gate. Therefore, a tradeoff between the bias voltage and the HF dip time is required. Otherwise, the replacement of the hard mask by a film less sensitive to the HF dip would be a promising solution.

#### **Perspectives**

The interest of low-k SiCO spacer etching using a combination of  $H_2$  plasma and HF dip has been demonstrated. In an upcoming study, we will optimize the developed processes and extend to other low-k films.

#### **RELATED PUBLICATIONS:**

[1] N.Posseme et al, JVST B, 2018, https://doi.org/10.1116/1.5038617

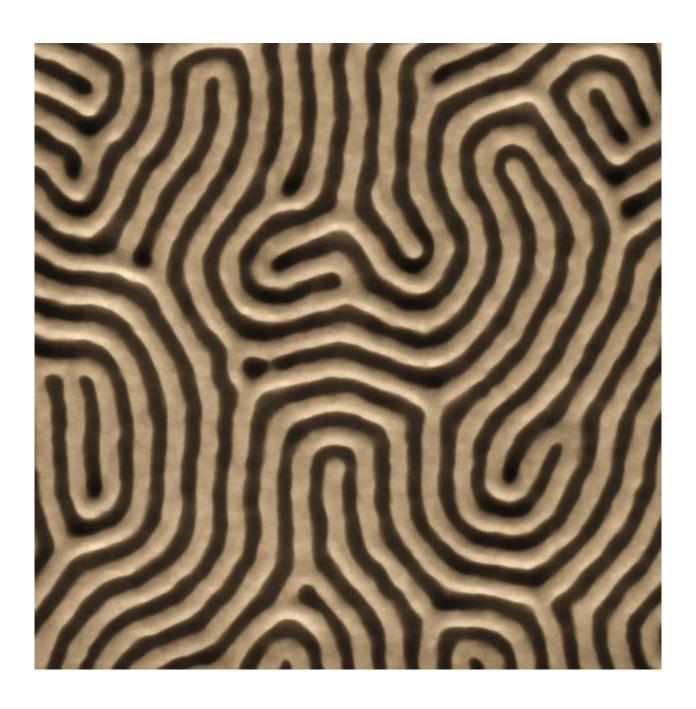

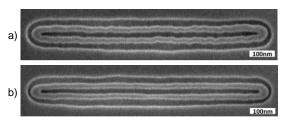

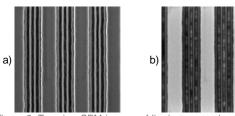

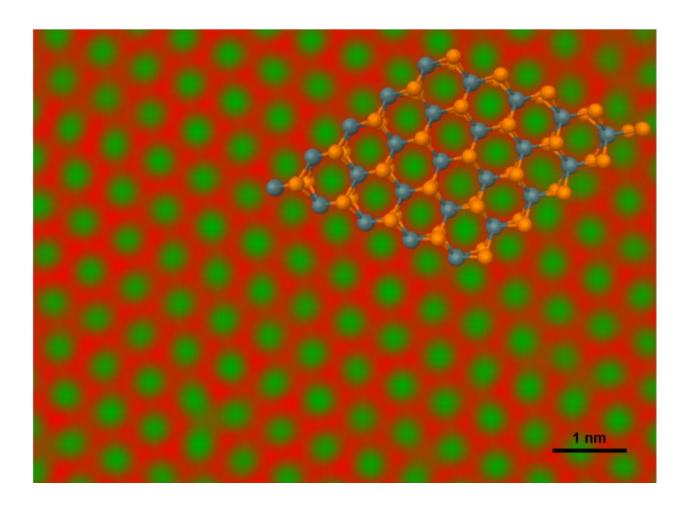

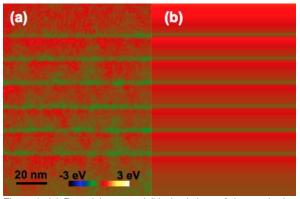

# **Fine-Tuning of Surface Energies for DSA Patterning**

#### **RESEARCH TOPIC:**

Advanced patterning, directed self-assembly, block copolymers

#### **AUTHORS:**

M. Argoud, G. Rademaker, P. Pimenta-Barros, A. Gharbi, Z. Chalupa, R. Tiron (R. Le Tiec), (S. Levi), (C. Navarro), (C.

#### **ABSTRACT:**

Directed self-assembly (DSA) of block copolymers (BCP) is a promising solution for advanced patterning of sub-10 nm technology nodes. Known for high-resolution capabilities, low-cost and ease process integration, DSA continues to attract the semiconductor industry. DSA technology is suitable for various patterning as line and space, contact shrink and multiplication and pillars. Recently, CEA-Leti has developed original DSA approaches from lab scale to industrial scale using its DSA pilot line and advanced BCP materials. The fine-tuning of surface energies and optimization of key lithographic parameters are reported.

SCIENTIFIC COLLABORATIONS: Arkema, Brewer Science, SCREEN, AMAT, LTM, LCPO, STMicroelectronics

#### **Context and Challenges**

Affordable, simple, versatile: DSA is still highly investigated as a sub-10 nm feature lithography technique to implement in the CMOS industry. DSA is used to target different lithography applications: creation of gratings of line and space, contact hole shrink and multiplication, and pillar patterning.

Firstly, in order to properly align the BCP, guide templates are created by conventional optical lithography. The surface energy of these guiding patterns, with respect to both monomers, needs to be finely tuned. Secondly, process parameters such as critical dimension uniformity (CDU), overlay and line roughness require to be optimized to meet stringent specifications.

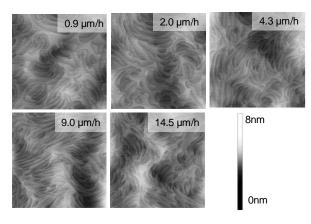

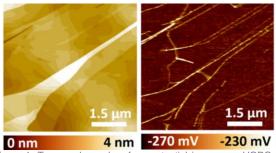

#### **Main Results**

Independent control of surface energy between the bottom and the sidewalls of a topographical guiding structure is critical for DSA process optimization.

For a contact hole shrink process, an embedded layer with tunable surface properties for DSA graphoepitaxy was evaluated and optimized [1]. A thin protective layer was placed between the hard mask guiding template and the embedded layer. This new layer allows to preserve the surface properties of the embedded layer during guiding template etching, resulting in better control of the polymer residual thickness (a few nanometers) and uniformity (< 1 nm) at the bottom of the guiding template. In turn, it will facilitate the subsequent DSA pattern transfer.

For a line/space graphoepitaxy DSA process, an innovative UVassisted method was developed for precise control of the surface energy of topographic grating [2]. Wafer-scale exposure of polystyrene (PS) lines using 193 nm wavelength radiation enables to reduce significantly the line roughness as illustrated in the Figure 1.

Figure 1: Top-view SEM images of PS lines transferred into 12nmthin single crystalline silicon (a) without any PS treatment, (b) with a PS treatment before etching.

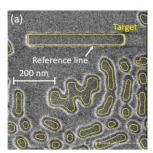

Advanced CD-SEM metrology utilizing the back-scattered electron imaging (BSE) mode [3] allowed to detect unwanted thin and buried polymer residues and subsequently to optimize the process (Fig. 2). This process has been integrated in a manufacturing flow of 22 nm lateral nanowire transistors, leading to an electrical demonstrator.

Figure 2: Top-view SEM images of line/space graphoepitaxy (a) with SE mode, (b) with BSE mode (brightness between lines indicates minimization of polymer residues).

#### **Perspectives**

The DSA team will focus on a novel approach to align the BCP by chemo-epitaxy and create the guides by sidewall image transfer (SIT). Line/space patterns with CDs of 15 nm down to 7 nm will be patterned. Control of surface energies and line roughness reduction are key elements to succeed.

- [1] F. Delachat et al., Nanoscale, 10 (23), 2018, <a href="http://dx.doi.org/10.1039/c8nr00123e">http://dx.doi.org/10.1039/c8nr00123e</a>

[2] P. Pimenta-Barros et al., in Proc. SPIE, 10584, 2018, <a href="https://dx.doi.org/10.1117/12.2297407">https://dx.doi.org/10.1117/12.2297407</a>

[3] R. Le Tiec et al., in Proc. SPIE, 10586, 2018, <a href="https://doi.org/10.1117/12.2299634">https://doi.org/10.1117/12.2299634</a>

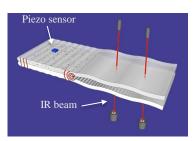

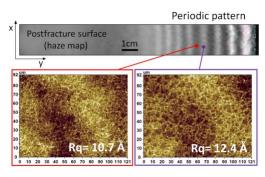

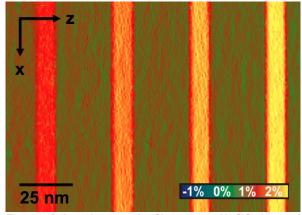

# **Pushing Line Roughness Metrology Techniques to their Limits**

#### **RESEARCH TOPIC:**

Line roughness, characterization, lithography

#### **AUTHORS:**

J. Reche, (M. Besacier), P. Gergaud, Y. Blancquaert

#### **ABSTRACT:**

The need for roughness metrology is recognized in the International Technology Roadmap for Semiconductors (ITRS). In order to reduce the edge or width roughness of lines, a metrology method is needed to quantify it. Firstly, roughness standard samples were manufactured and used as standards to evaluate the performances of several metrology tools. The capability of each of these roughness measurement techniques was evaluated in terms of resolution, access to frequency information, acquisition and treatment throughput, and maturity.

**SCIENTIFIC COLLABORATIONS: CNRS/LTM**

#### **Context and Challenges**

The control of line roughness presents a huge challenge for the lithography step in the semiconductor industry. For advanced nodes, this morphological aspect reaches the same order of magnitude than the Critical Dimension (CD), which leads to an increased power consumption by transistors and devices. For the 7 nm node, the acceptable roughness is only 0.7 nm, which means that the resolution of the measurement has to be at the angstrom scale. Hence, an adapted metrology is required for the control of roughness. The current technique for CD analysis and roughness extraction is the Critical Dimension Scanning Electron Microscopy (CD-SEM), but many other metrology techniques as Atomic Force Microscopy, Small-Angle X-ray Scattering (SAXS) and Optical Scatterometry (OCD) are also developed.

#### Main Results

First of all, roughness standard samples were manufactured [1]. The preliminary steps were to demonstrate the patterning methodology and the line roughness metrology, using periodical roughness samples.

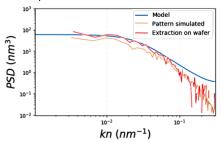

Figure 1: Example of programming roughness with PSD plots obtained through: model calculation, simulation of SEM images and experimental measurements

Further, programming of roughness based on Power Spectral Density (PSD) with Auto-Correlation Function (ACF) model was

used to achieve roughness close to a real roughness case (Fig.1). The samples have been written using e-beam lithography taking into account the specific constraints of the different metrology techniques.

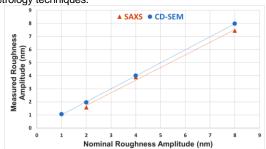

Figure 2: Extracted roughness amplitude with CD-SEM and SAXS compared at nominal roughness amplitude

These specific lines gratings programmed samples were characterized with three different methodologies [2], CD-SEM, OCD and SAXS and compare in terms of roughness resolution, access to frequency information, acquisition and treatment throughput and maturity. This comparison highlights that (i) OCD can detect roughness but needs calibration, (ii) CD-SEM and CD-SAXS give similar results (Fig. 2), close to the nominal roughness values designed.

#### **Perspectives**

The next step for sample manufacturing is to integrate within the design the natural line roughness in order to avoid reference subtraction and so to obtain real standard samples. We are also working on data fusion of the different techniques CD-SEM/CD-SAXS/OCD. The development of a line roughness hybrid metrology using neural network is in progress that will exploit the strengths of each methodology.

- [1] J. Reche et al., 34th European Mask and Lithography Conference, 2018, -http://dx.doi.org/10.1117/12.2327095 [2] J. Reche et al., Journal of Micro/Nanolithography, MEMS, and MOEMS 17 (4), 2018, http://dx.doi.org/10.1117/1.JMM.17.4.041005

#### **Lithography Computational Aspects** for Mask Writing

#### **RESEARCH TOPIC:**

Computational lithography, mask data preparation, proximity correction, computational metrology

#### **AUTHORS:**

L. Audebert, S. Bérard-Bergery, (J. Bustos), A. Fay, A. Forier, J. Hazart, J.B. Henry, A. Girodon, E. Guyez, L. Perraud, J. Pradelles, P. Quéméré.

#### **ABSTRACT:**

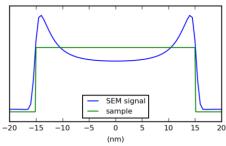

Optical lithography for advanced nodes uses complex Optical Proximity Corrections (OPC) resulting in sub-100 nm curvilinear mask patterns. A dedicated small-shots correction was developed to substantially improve the fidelity of demanding aggressive mask patterns written directly with Variable Shaped Beam (VSB) e-beam technology. Additionally, in-line 3D metrology is of key importance to further improve and control the lithography processes. We demonstrate that model-based Scanning Electron Microscope (SEM) 3D non-destructive metrology is a promising in-line technology to reconstruct 3D topography with a rather high precision despite the typical SEM noise level.

SCIENTIFIC COLLABORATIONS: ASELTA Nanographics, Université Grenoble Alpes LJK

#### **Context and Challenges**

Inverse Lithography Technology (ILT) and advanced photonics patterns push e-beam VSB mask writing technology to its limits. Beyond 50 nm resolution, small VSB shots are not well controlled due to machine imperfections inducing mask patterns errors. A specific mask data preparation (MDP) solution is proposed to overcome these errors. On the other hand, lithography process optimization for 3D complex architectures is demanding of accurate in-line 3D metrology. The ultimate accuracy of the reconstructed 3D geometry by model-based SEM 3D metrology is reported.

#### **Main Results**

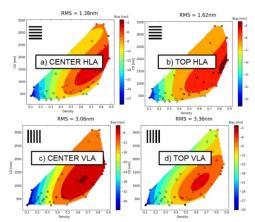

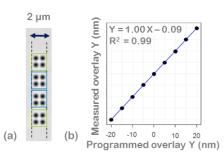

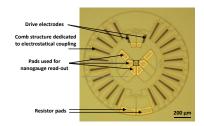

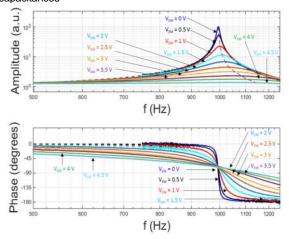

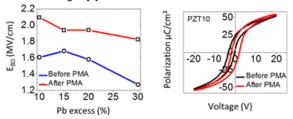

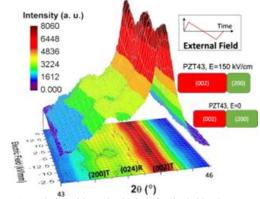

#### New small-shots correction for Mask Data Preparation