## TECHNOLOGY RESEARCH INSTITUTE

#### **LETI AT A GLANCE**

Founded in 1967

Based in **France** (Grenoble) with offices in **USA** (Silicon Valley) and **Japan** (Tokyo)

350

industrial partners

1,900

researchers

Committed to innovation, Leti's teams create **differentiating solutions** in miniaturization and energy-efficient technologies for its industrial partners.

Leti is a technology research institute at CEA Tech and a recognized global leader focused on miniaturization technologies enabling energy-efficient and secure IoT. Leti delivers solid expertise throughout the entire IoT chain, from sensors to data processing and computing solutions. Leti pioneered FDSOI low power platform for IoT, M&NEMS technology for low cost multisensors solutions, CoolCube™ integration for highly connected and cost effective devices.

Leti's mission is to pioneer new technologies, enabling innovative solutions to ensure Leti's industrial partners competitiveness while creating a better future. It tackles most current global issues such as the future of industry, clean and safe energies, health and wellness, sustainable transport, information and communication technologies, space exploration and safety & security.

For 50 years, the institute has built long-term relationships with its partners: global industrial companies, SMEs and startups. It tailors innovative and differentiating solutions that strengthen their competitiveness and contribute to creating new jobs. Leti and its partners work together through bilateral projects, joint laboratories and collaborative research programs. Leti actively contributes to the creation of startups through its startup program.

Leti has signed partnerships with major research technology organizations and academic institutions. It is a member of the Carnot Institutes network\*.

\*Carnot Institutes network: French network of 34 institutes serving innovation in industry.

2,670

patents in portfolio

60

startups created

**€315**

million budget

700

publications each year

ISO 9001

certified since 2000

Within CEA Tech and Leti, silicon technologies and components research activities are shared between two divisions gathering together around 600 researchers:

**The Silicon Technologies Division** carries out innovative process engineering solution and research, operates 24/7 year round, 7,500m2 of state-of-the-art cleanroom space divided into three different technology platforms.

**The Silicon Components Division** carries out research on nanoelectronics and heterogeneous integration on silicon and is focusing on two mains areas: on-going shrinking of CMOS devices to extend Moore's Law for faster, less-expensive computing power, and the integration of new capabilities into CMOS, such as sensors, power devices, imaging technology, and new types of memory, to enable new applications.

This booklet contains 47 one-page research summaries covering advances in the focus areas of our Silicon Devices and Technologies Divisions, highlighting new results obtained during the year 2015.

....

п

. .

:: =

н

н

п

.

=

11

..... 111

ш

. .

. . .

н ш ш

.... ш

ш

## Contents

| Edito                                               | 04 |

|-----------------------------------------------------|----|

| Key figures                                         | 11 |

| Silicon Divisions & Platforms                       | 12 |

| Scientific activity                                 | 15 |

| 01 / Core & Beyond CMOS                             | 17 |

| 02 / Memories                                       | 23 |

| 03 / Patterning                                     | 29 |

| <b>04 /</b> Energy                                  | 35 |

| 05 / Modeling & Simulation                          | 39 |

| 06 / Passive & RF Components                        | 45 |

| 07 / MEMS Actuators & Sensors & Reliability         | 51 |

| 08 / 3D Integration & Packaging                     | 59 |

| 09 / Physical-chemical Characterization & Metrology | 65 |

| 10 / Emerging Process                               | 73 |

| PhD Degrees awarded in 2015                         | 79 |

### **Edito**

#### Thomas ERNST Chief Scientist

#### Dear Reader

We are proud to release our seventh Silicon Components and Technologies Annual Scientific Research Report, for the year 2015. This booklet contains 47 one-page research summaries covering advances in the focus areas of our Silicon Components and Technologies Divisions, highlighting new results during the year.

The year 2015 illustrates the strong diversification of nanotechnologies at Leti and in particular in our Si technologies departments for emerging applications such as the Internet of Things (IOT), automotive, energy and health monitoring.

In 2015, the Silicon Divisions produced 426 publications, including 109 in peer-reviewed journals, achieving impact factors as high as 31.

Our sensor research activities were established more than 25 years ago with a first startup creation in 1997. Since then, we have transferred several technologies to our startups or to established companies worldwide. The combination of new materials and architectures, and our vision ranging from emerging materials to systems enable us to propose competitive solutions for emerging applications. Our research on future IoT sensing systems includes embedded RF functionalities, dedicated packaging (especially for harsh environments), energy harvesters and micro-batteries.

We are also anticipating new paradigms in data treatments. Moore's Law will reach its end around 5 nm. However there is a strong need in the emerging "big data" society to make our systems more energy efficient by one order of magnitude or even more. Such breakthroughs should combine both hardware and software innovations. This trend is illustrated in this report by neuromorphic computing. Such research includes new materials (for resistive RAM), and 3D integrations. In our approach, those technological breakthroughs remain compatible with existing technologies. Thin films technologies such as FDSOI, nanowires and 2D materials are also a key element for future ultralow-power technologies.

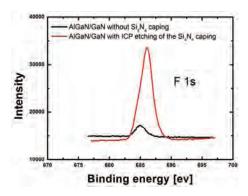

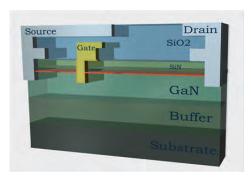

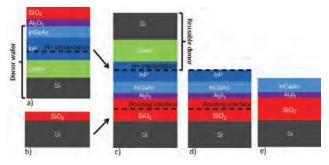

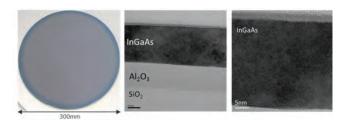

New materials stimulate our innovation for growing domains, such as automotive, energy, data transfer... We also outline this year our results on GaN transistors on Si for power devices, GeSn laser, first 300 mm InGaAs-on-insulator substrates and innovative processes for 2D materials growth. Our divisions develop advance processes to pattern those materials at the nanoscale including DSA, nanoimprint and advanced maskless lithography.

We are very proud of our valuable collaborations with nearly all of French universities, CNRS laboratories and research institutes involved in nanotechnologies for electronics.

Our visibility and international recognition are made possible by our international collaborations including teams at Jülich (Germany), Tokyo Institute of Technology (Japan), Stanford (USA), Caltech (USA), the University of California (USA), University of Cambridge (GB), École Polytechnique Fédérale de Lausanne (Switzerland), CNR (Italy), Sherbrooke University (Canada) and Albany-Nanotech (USA); and by our participation in major international conferences through technical program committees, boards of governors and evaluation committees.

We thank all our industrial partners for their continuing confidence in us. We are committed to ensuring the transfer of our research to industry. Strong industrial partnerships are the foundation of our culture of innovation.

Underlying all these efforts is the cooperation of all our researchers and management, as well as the Silicon Technologies and Components Divisions and Leti's scientific advisory boards.

I wish to thank my predecessor Simon Deleonibus, now retired, for his continuous efforts to introduce new topics and ideas and encouraging researchers to explore new fields.

I also wish to extend my appreciation to the 10 chapter editors and authors of the 2015 Scientific Report, who spared no effort to prepare this document.

Thomas Ernst Chief Scientist

#### **Edito**

#### Jean-René LEQUEPEYS

Head of Silicon Components Division

#### Dear Reader

Semiconductor industry growth is slowing and outlooks are mixed for the next few years, largely because of the fragile global economic outlook. This creates uncertainties about:

- Technology roadmaps: a co-existence between FDSOI and FinFET? Which R&D strategy for 450mm? What will be the impact of non-volatile memory emerging technologies? When will a new era of computing based on neuromorphic or quantum electronics arrive?

- Collaborative models or alliances: increase in number of large mergers, growth of the Chinese ecosystem, IDMs refocusing on their core business ...

- Development of future markets: advanced driver assistance systems, Internet of Things, Big Data, High Performance Computing and servers, e-health ...

In this evolving context, our division reaffirms its world-leading position in nanoelectronics research, and it delivered again in 2015 cutting-edge technology solutions to its industrial partners. The following is a partial list of our major breakthroughs of the past year.

#### **CMOS**

- Leti helped STMicroelectronics extend its offer in 28nm FDSOI with a variety of key technology blocks, such as memories and RF, targeting Internet of Things applications.

- Leti assigned a team of experts to GLOBALFOUNDRIES' Fab 1 in Dresden to support ramp up of the 22FDX<sup>™</sup> technology platform. As an ecosystem partner, Leti is also providing GLOBALFOUNDRIES' customers circuit-design IP, including its back bias feature for FDSOI, which enables exceptional performance at very low voltages with low leakage.

- EV Group (EVG) joined the 3D integration consortium of IRT Nanoelec, which is headed by Leti. EVG joins Leti, ST and Mentor Graphics to develop advanced 3D wafer-to-wafer bonding technologies. SET also joined the consortium this year.

- Leti is continuing its path finding solutions to future nanoelectronics technologies and systems; noteworthy results were achieved in quantum computing and neuromorphic architectures.

#### **Power Electronics and Energy**

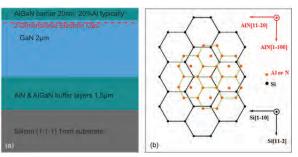

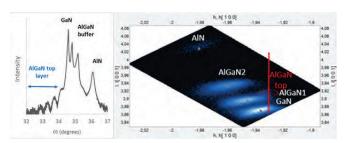

- Major improvements have been made on our HEMT Normally-Off power transistors. Last year, our 200mm GaN-on-silicon technology convinced several industrial partners to commit to longterm partnerships with us.

- Our start-up Exagan raised €5.7 million to produce high-efficiency GaN-on-Silicon power-switching devices on 200mm wafers. This Leti and Soitec spinout is focusing on becoming a leading European source of GaN devices for solar, automotive, telecoms and infrastructure uses.

- CEA Tech and Fraunhofer ISE signed a collaboration agreement to create a common "virtual lab". We will combine forces in "industry-like" research to further develop high efficiency multijunction solar cells, educate young scientists and develop prototypes of next-generation ultra-high-efficiency solar cells.

#### **Microsystems**

- We manufactured micro-accelerometers on 300mm wafers, a first for the MEMS industry. This development could lead to significantly lower MEMS manufacturing costs.

- We provided support to our startup WAVELENS which is developing optical MEMS solutions aimed at improving camera image quality by making the integration of optical functions such as autofocus, image stabilization and zoom, easier.

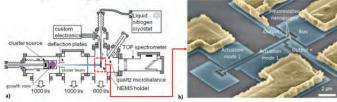

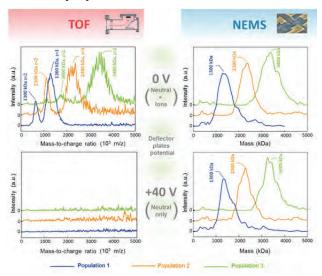

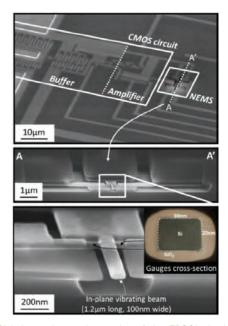

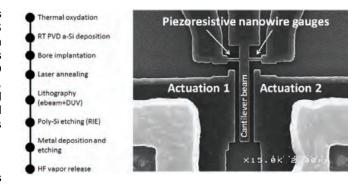

- We demonstrated a NEMS-CMOS co-integration based on our CoolCube<sup>™</sup> technology. Scaling down dimensions also scales down the amplitude of the signals and susceptibility to parasitics, in particular for resonant NEMS sensing. CMOS co-integration is the only viable solution to this complex addressing issue. Moreover, a vertical integration, as offered by CoolCube<sup>™</sup>, can be a competitive advantage for footprint reductions of MEMS sensors.

All these results were obtained due to the sustained efforts of our team, and I would like to sincerely thank them all. This report provides you with an overview of their achievements.

Jean-René LEQUEPEYS

Head of Silicon Components Division

#### **Edito**

#### **Fabrice GEIGER**

Head of Silicon Technologies Division

#### Dear Reader

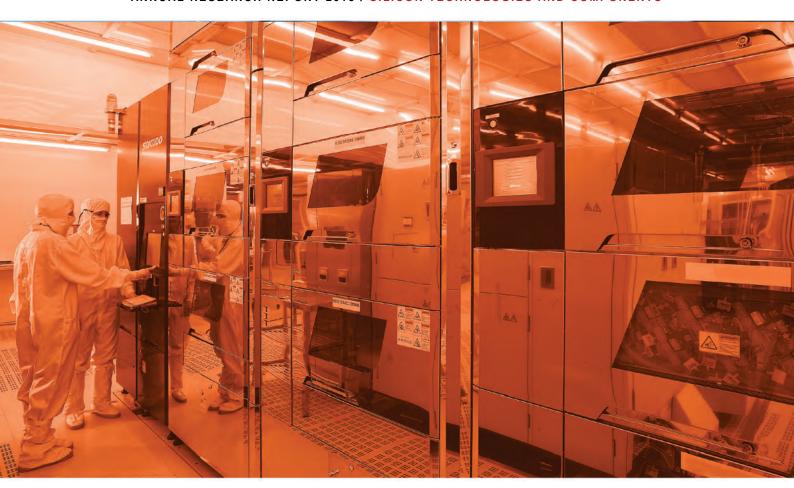

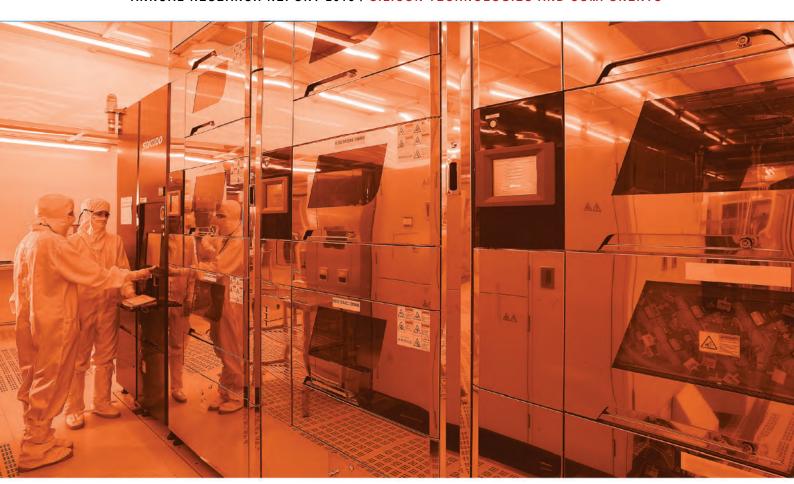

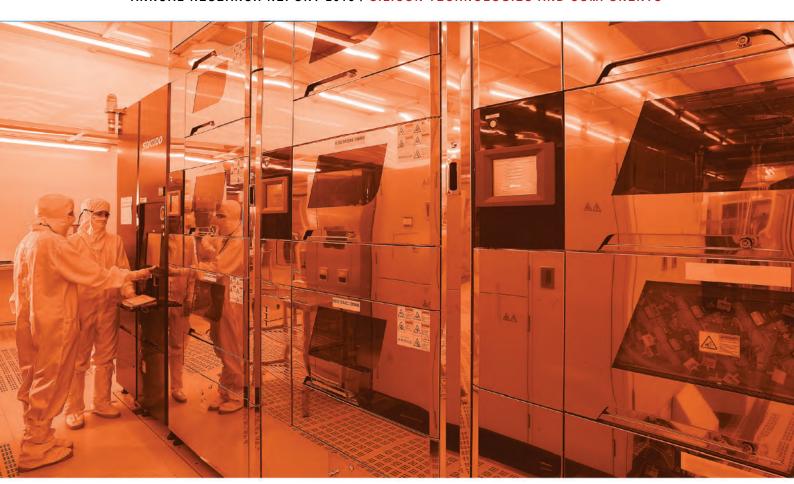

The mission of our division is to provide our internal and external customers with the best innovative engineering solutions, so they can perform world-leading research on next-generation technology nodes. To achieve this, we provide 7,500m² of advanced research facilities, 3,000m² of nano characterization platform and the best human competencies.

In 2015, we invested €32.4M investment in new manufacturing equipment. This figure includes €7.9M dedicated to upgrading our installed base. Examples of tools put into production last year include a 300mm Applied Endura platform for PCRAM, an Applied Verity tool for high-volume metrology of logic and memory devices and a new LAM KIO FX etcher tool for tiny conductor and for III-V materials etching for photonics and a stepper CANON FPA 5510iZ for our 3D integration line.

This internal investment is complemented by a strong policy of collaboration with tool manufacturers. The idea is to build win-win partnerships. Leti takes advantage of innovative tools or materials to develop next-generation technologies. In return, our partners gain insight into the requirements needed for future market positioning.

We renewed four common labs in 2015:

- With EV Group (EVG): a new program in nano-imprint lithography (NIL) called INSPIRE to demonstrate the benefits of the versatile, powerful nano-patterning technology.

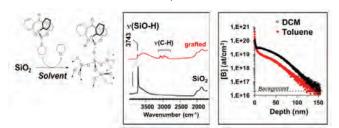

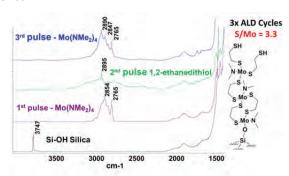

- With Aveni (former Alchimer) a project to develop their innovative approach to metallization for semiconductor, MEMS, advanced packaging and flex applications. Aveni's processes-Electrografting and Chemicalgrafting-rely on molecular engineering to grow metallization films molecule by molecule.

- With SPTS to develop disruptive 300mm HAR Cu-filling technology using CVD Cu-seed process in our 3D integration line.

- With Mapper Lithography to develop the ecosystem around multi-beam lithography. We installed the MATRIX pre-production equipment and were able to qualify this new and disruptive maskless technology.

We also strengthened and extended strategic partnerships with major manufacturing equipment suppliers as Applied Materials, LAM research, Tokyo Electron (TEL), Screen Semiconductor Solutions and FEI.

The year also was rich in scientific results for our division with a record number of more than 290 scientific papers published. The international recognition we received (seven distinctions and awards obtained in 2015) underscores the excellence of our teams and their accumulated skills and expertise. We have also generated 41 patents.

Our teams are focusing on key challenges around advanced CMOS, 3D, photonics and advanced memories. We are also addressing key 200mm challenges around MEMS, power electronics, RF, magnetic materials and other fields. Examples of our achievements include:

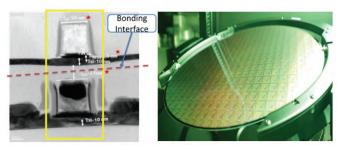

- Demonstration of a ultra-high vacuum direct bonding activated by ion beam. Examples of applications are heterogeneous integration (e.g. multi-junction solar cells based on III-V semiconductors), layer transfer for advanced substrates or high-vacuum encapsulation (MEMS).

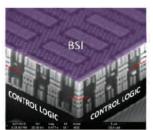

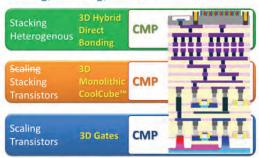

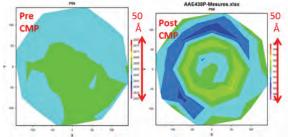

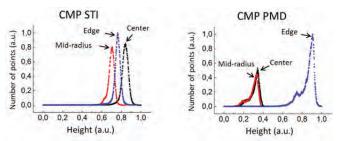

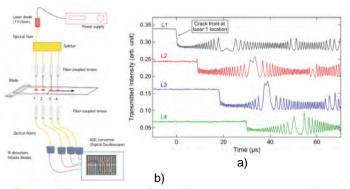

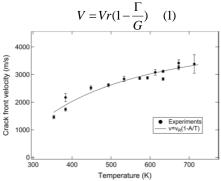

- Development of an industrial CMP process for direct hybrid bonding and its application to 3D advanced imagers with direct assembly of Back Side Illuminated (BSI) wafers on the display processor. Direct hybrid bonding is quite promising for 3D industry because it enables very high interconnection densities compare to standard thermos-compression packaging technologies.

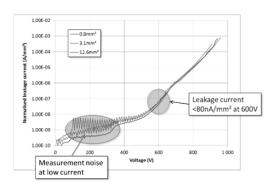

- Development of a methodology that allows a rapid evaluation of GaN-on-Si epitaxial wafers and does not involve any sample preparation. It enables our team to drastically lower the hole defect density, thus increasing the blocking voltage limit. As a consequence GaN power devices up to 12mm² (corresponding to devices capable of passing 90A) can be produced with no impact on the leakage current.

This scientific annual report includes additional details about all these key achievements, which were made possible by the work of our researchers and technicians. I would like to take this opportunity to thank all of them for their constant commitment.

Fabrice Geiger Head of Silicon Technologies Division

#### ANNUAL RESEARCH REPORT 2015 / SILICON TECHNOLOGIES AND COMPONENTS

## **Key figures**

607 Permanent staff220 Industrial residents

119 PhD students

22 Post-docs

200&300mm Platforms for CMOS

7,500 m<sup>2</sup>

**500**

and MEMS

Clean rooms

Process tools

Non-stop operation

**121** Patents filed in 2015

426 Scientific papers produced

- 17 Common laboratories

- 7 Startups created since 2010

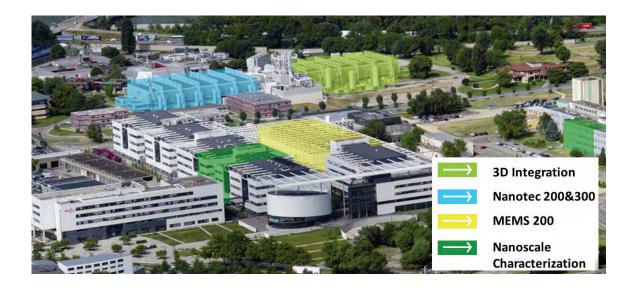

## **Technological Platforms**

**The silicon divisions** operate 7,500m² of state-of-the-art cleanroom space divided into three platforms, gathering 500 process tools and a combined staff of more than 450; they run industry-like operations, 24 hours a day, 7 days a week, all year round.

- The Nanotech200&300 platform provides 200mm and 300mm CMOS wafer processing, which can be applied to both semiconductor and microsystem devices.

- The MEMS200 platform produces non-CMOS Micro-ElectroMechanical Systems (MEMS).

Both platforms are focused on the More than Moore initiative to develop new semiconductor capabilities. An innovative cleanroom shuttle system links the two platforms to add process flexibility and faster processing.

- The third platform 3D Integration aims to integrate various microelectronics objects together in order to juxtapose complementary functions, such as sensing, storing, processing, actuation, communication and energy scavenging. This provides advanced system solutions in three dimensions. This line is open to our customers for prototyping through the Open3D service.

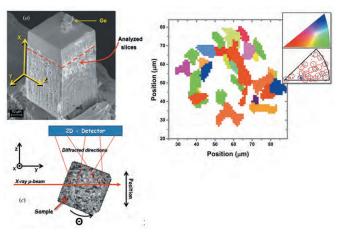

- All research carried out in our cleanrooms benefits from the Nano-Characterization Platform, which is located on the MINATEC campus. This platform, unique in Europe, covers eight domains of competencies, including electron microscopy, X-ray diffraction, ion beam analysis, optics, magnetic resonance, scanning probe, surface analysis and sample preparation.

## **Organization**

Silicon Technologies Division is organized according to six departments.

- Three Process Departments whose missions are to realize generic process steps for all projects and to develop innovative processes to provide state-of-the-art solutions to internal and external customers. Those departments are focused on patterning, deposition, and surface treatments. Their research activities in collaboration with key universities will support Leti's advanced position in the future.

- A Characterization Department whose mission is to perform off-line observations to characterize process steps, materials or components. This department also has a research activity to maintain its level of excellence.

- Two Support Departments: one is in charge of the planning, the interface with internal divisions or external customers as well as methods, training and clean-concepts. The other is responsible for facilities operations and engineering.

**Silicon Components Division** is organized around three departments with clear objectives and market focus.

- The MOS Department's mission is to simulate, model, develop, demonstrate and test new generations of circuits and modules for sub-20nm CMOS, digital and memory.

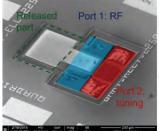

- The MEMS Department designs and develops innovative microsystem components (sensors, actuators and RF) and the associated toolbox (packaging, heterogeneous integration, reliability).

- The Power and Energy Department develops and demonstrates technology modules and components for power and energy (photovoltaic, power electronics, integrated storage).

#### ANNUAL RESEARCH REPORT 2015 / SILICON TECHNOLOGIES AND COMPONENTS

## **Scientific Activity**

#### **Publications**

- In 2015: 426 publications produced

- Ratio "A grade published items/ Publishing researchers"> 1.00 (including grade A conferences, journals and international extended patents)

#### **Distinctions and Awards**

- 8 distinctions and awards received in 2015

- Young Scientist Award –E-MRS 2015, L. Bonnet

- Young Scientist Award –E-MRS 2015, D. Ouhab

- Best Video Clip Award –Bronze Medal -JSIAM 2015, L. Bonnet

- Prix IEEE EDS Paul Rappaport 2015, V. Delaye, D. Lafond, J.-M. Hartmann

- Young Scientist Award –M&M 2015, R. Estiville

- Best Paper Award -IWJT 2015, E. Ghegin

- Prix NanoArt2015, V. Gorbenko, T. Printemps

- Best student paper SISC 2015, Julien Borrel

- 84 additionnal awards including the 2005 Grand Prix Académie des Technologies, 2008 IEEE Cledo Brunetti Award, 2011 French-German Prize for Economy, 2011 Silver Medal STMicroelectronics, 2012 SEE Grand Prix du Général Ferrié, 3 ERC grants, 49 Best Papers Awards

#### **Expertise and Recognitions**

- 97 Leti experts: 4 Research Directors, 7 International Experts

- 25 researchers with habilitation qualification "HDR" (to independently supervise doctoral candidates)

- 1 IEEE Fellow, 3 IEEE Seniors

#### **Scientific Committees**

- 3 journal editors: IEEE TED, European Physical Journal-Applied Physics, Science China-Information Sciences

- 7 researchers involved in ITRS (International Technology Roadmap for Semiconductors)

- 40 members of Technical Programs and Steering Committees at major conferences: IEDM, VLSI Technology Symposium, IRPS, ESSDERC, SSDM, ECTC, ECS...

- Awards committees: IEEE Cledo Brunetti Award, IEEE Paul Rappaport Award, SEE & IEEE Brillouin-Glavieux Award, European Research Council Panel

- Boards of Governors: IEEE ED Society, Nanosciences Foundation Board, IEEE CPMT, SFV IEEE ED Society Region 8 Vice-Chair

#### International Collaborations

Collaborations with more than 50 universities and institutes worldwide: Tokyo Institute of Technology (Japan), CALTECH (USA), University of Stanford (USA), University of Berkeley (USA), University of Cambridge (GB), University of Tokyo (Japan), EPFL (Switzerland), Albany-NT (USA), ...

# O1 CORE & BEYOND CMOS

- 14nm FDSOI Technology for Energy Efficient CMOS

- Innovative Strain Techniques for CMOS Performance Boosting

- From Mismatch to Process Variations A Unified CAD-Compatible Model of Statistically Correlated Variability

- Tungsten and Copper Interconnection Stability for 3D VLSI CoolCube<sup>TM</sup> Integration

- Nanowire MOSFET for 5nm Node and Beyond

#### 14nm FDSOI Technology for Energy Efficient CMOS

Research topics: CMOS, SOI

O. Weber, J. Mazurier, P. Perreau, F. Andrieu

#### Partnership: STMicroelectronics Sponsorship: NANO 2017, ENIAC-Places2Be

#### Context

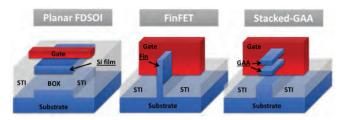

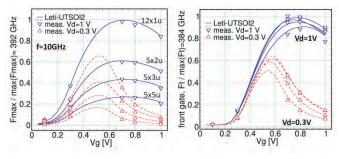

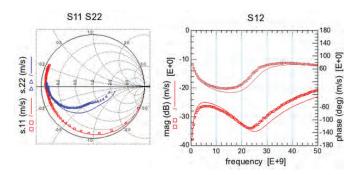

As CMOS technology scales down, two paths are pursued by the industry to overcome the fundamental limits of traditional planar bulk transistors. One is the introduction of a Tri-Gate or FinFET transistor at the 22 and 16-14 nm nodes. These architectures provide impressive drive currents per footprint at low supply voltages because of the 3-D conduction channel and excellent electrostatic control. Conversely, they have high gate and parasitic capacitances, proportional to the 3-D effective W increase, which negatively impacts both the speed and active power consumption. Alternatively FDSOI provides an evolutionary path. First introduced at the 28nm node, FDSOI includes excellent mismatch properties, a simplified planar manufacturing process vs 3-D finFET technology and capitalization of existing design techniques. It also extends the possibility of back biasing and therefore offers unique "smart" solutions for dynamic power optimization. The technology reported here furthers the appeal of FDSOI to the 14nm node [1].

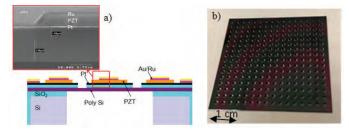

#### **Process Technology**

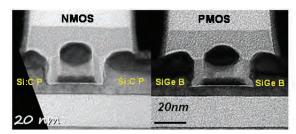

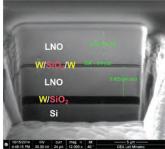

Table 1 highlights key 14nm FDSOI design rules and technology features. A 0.55x area scaling with respect to the 28nm FDSOI technology was achieved with the introduction of local interconnect and the adoption of fixed layout shapes (or "constructs"). Compared to the 28nm technology, new front-end process elements include a dual SOI/SiGeOI N/P channel, a dual workfunction gate-first HKMG integration scheme and a dual in-situ doped Si:CP/SiGeB N/P raised source-drain (Fig.1). Additionally, and for the first time, a SiBCN low-k material spacer was integrated in a gate-first flow for minimizing the gate-to-drain parasitic capacitance [1].

| Key features                 | 28FDSOI             | 14FDSOI              |

|------------------------------|---------------------|----------------------|

| Min Contacted gate pitch CPP | 114nm               | 90nm                 |

| M1 pitch                     | 90nm                | 64nm                 |

| Std cell area                | 1X                  | 0.55X                |

| VT flavours                  | RVT / LVT           | LVT / SLVT           |

| Lgate in min CPP             | 24nm → 30nm         | 20nm → 34nm          |

| Channel                      | SOI 7nm             | Dual SOI/SiGeOI 6nm  |

| Buried oxide                 | BOX 25nm            | BOX 20nm             |

| Gate                         | HKMG single metal   | HKMG dual WF         |

| Source-Drain                 | Single Si epi + I/I | Dual epi SiGeB/Si:CP |

Table 1: Key 14FDSOI ground rules and technology features.

Figure 1: N&PMOS transistor TEM cross-sections in 14nm FDSOI.

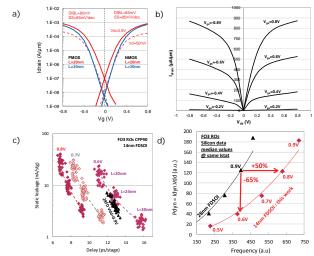

Figure 2: (a)  $I_d(V_g)$  for N&PMOS transistors at L=20nm and 30nm,  $V_{od}$ =0.8V, (b)  $I_d(V_d)$  for N&PMOS transistors at L=20nm and Vdd=0.8V, (c) 14nm FDSOI Delay/Istat for FO3 ring oscillators vs 28nm FDSOI, (d) 14nm FDSOI Frequency/Pdyn vs 28nm FDSOI.

#### **Performance & Power**

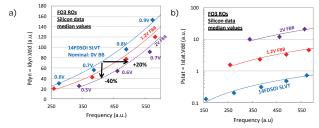

$I_d$ - $V_q$  plots at  $V_{dd}$ =0.8V show DIBL of 85mV and a subthreshold slope of 85mV/dec. for both NMOS and PMOS at  $L_{nom}$ =20nm (Fig.2a).  $I_{dsat}$ =880 $\mu$ A/ $\mu$ m at  $I_{off}$ =100nA/ $\mu$ m and V<sub>dd</sub>=0.8V were achieved at L<sub>nom</sub>=20nm/W<sub>nom</sub>=0.17μm for both NMOS and PMOS (Fig.2b). As a result, 14nm FDSOI devices running at  $V_{dd}$ =0.6 $\overline{V}$  are as fast as 28nm FDSOI devices running at V<sub>dd</sub>=0.9V (Fig.2c). At the same operation frequency and at same static leakage, 14nm FDSOI provides 65% power saving over the 28FDSOI technology (Fig.2d) [1]. In addition, FDSOI offers a unique opportunity for energy efficient product design in its extended capability of back biasing. Fig.3a shows that devices running at V<sub>dd</sub>~0.63V with a 2V forward back bias (FBB) are as fast as devices running at V<sub>dd</sub>=0.8V with no back bias, reflecting a 40% dynamic power saving at same speed. Of course, because FBB is associated with V<sub>t</sub> lowering, static leakage strongly increases at the same time, as shown in Fig.3b. But, with this flexibility offered by the large back bias capability, FDSOI appears as a powerful technology to find the right performance at the right power and at the right leakage for each application product.

Figure 3: Freq/Pdyn (a) and Freq/Pstat (b) with forward back bias application.

#### Related Publications

- [1] O. Weber et al., "14nm FDSOI Upgraded Device Performance for Ultra-Low Voltage Operation", VLSI Technology Symposium, 2015.

- [2] O. Weber et al., (invited) "Static and Dynamic Power Management in 14nm FDSOI Technology", ICICDT conference, 2015.

- [3] O. Weber et al., (invited) "14nm FDSOI Technology for High-Speed and Energy-Efficient CMOS", ECS transactions 2015 issue 20.

#### **Innovative Strain Techniques for CMOS Performance Boosting**

Research topics: Strain, Stress, CMOS, Si, SiGe, SOI, sSOI, BOX Creep, STRASS

C. Le Royer, S. Reboh, Y. Morand (STM), A. Bonnevialle (STM), D. Rouchon, P. Gergaud, C. Plantier, J.-M. Hartmann, O. Rozeau, S. Maitrejean, B. de Salvo

Partnership: STMicroelectronics

Sponsorship: IRT Nanoelec., ECSEL-WayToGoFAST

#### **Context and Challenges**

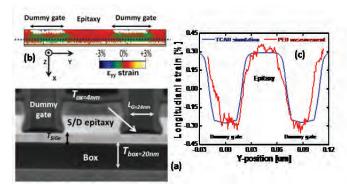

Innovative performance boosters (mainly strain boosters) are mandatory to improve Fully-Depleted SOI devices performance and power efficiency. Channel strain is an effective way to enhance electrons and holes mobility: compressive SiGe for pFETs and tensile Si for nFETs. The interest of using Smart Cut<sup>TM</sup> sSOI substrates (for nFETs), SiGe channels/Raised Sources and Drains (for pFETs) as strain boosters has successfully been demonstrated on FDSOI architecture.

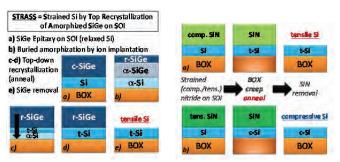

Since 2013 we investigate new strain techniques [4] such as "<u>STRASS</u>" (Fig.1.i) [1,2] and "<u>BOX creep</u>" (Fig.1.ii) [3] in order to obtain tensile stress (for nFETs) and compressive stress (for pFETs).

Figure 1: i) Schematics of the STRASS process to fabricate tensile Si on insulator. ii) Principle of the BOX creep technique applied to the fabrication of a) tensile Si and b) compressive Si, depending on the sacrificial SiN stress.

#### **Main Results**

<u>STRASS for tensile Si</u> [1]: We propose here another approach (Fig.1.i) to create sSOI structures starting from SOI ones by transfer of lattice parameter from a relaxed  $Si_{0.7}Ge_{0.3}$  to the Si layer. The process is divided in four steps: i) a  $Si_{0.7}Ge_{0.3}$  epitaxy of 40 nm on SOI with 9 nm thickness Si; ii) an amorphization by Si implantation at 25 keV with 2.5 x  $10^{14}$  at/cm² (tilt 0°) of the Si layer and the lower portion of the SiGe layer; iii) a recrystallization by thermal annealing at 850 °C, 10 s under N2 atmosphere, and; iv) SiGe selective etching using HCI. The stress induced in the Si thin film is memorized turning the initial SOI into sSOI. According to Raman spectroscopy, the 9 nm Si layer exhibits a large tensile stress (+1.6 GPa), which is expected to lead to a +60% in electron mobility (at 1MV/cm electric field).

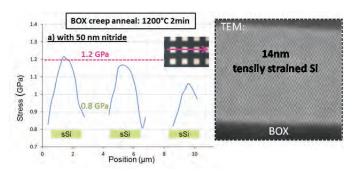

BOX creep for compressive Si (or SiGe) [3]: We demonstrate in 2015 the fabrication of localized tensily strained Si-On-Insulator (sSOI) using a method named BOX creep process. This technique is based on the creep of the Buried OXide (BOX) and consists in the stress transfer from a top sacrificial (compressive) SiN layer into the thin Silicon layer during a high temperature anneal (Fig.1.ii.a). Strain and stress were determined using Raman spectroscopy. Using a compressive SiN on SOI (14 nm Si / 145 nm BOX), we turned relaxed Si into tensile Si with +1.2 GPa stress.

Figure 2 : Left) Stress profiles from scanning Raman extractions for 2x2µm² SOI structures after BOX creep process. Right) Corresponding cross-sectional HAADF STEM micrograph of the sSi film.

We have also investigated the crystalline quality and the top Si roughness of the fabricated sSOI MESAs. The cross sectional STEM micrograph (Fig.2.ii) of the Si layer after BOX creep process confirms the good crystallinity of silicon: no defects are observed in the field. All the AFM mapping measurements confirm the absence of impact of this technique on the Si roughness.

#### **Perspectives**

After the morphological studies which enabled to confirm the strain efficiency of these techniques, we are currently investigated the integration of STRASS and BOX creep modules in a state-of-the-art FDSOI CMOS route. The goal of these electrical demonstrations is to obtain significant boost in the electrical performance of the fabricated devices and circuits. Moreover we will be able to optimize process conditions and to tackle the potential design issues related to STRASS and BOX creep.

#### Related Publications

[1] A. Bonnevialle, S. Reboh L. Grenouillet, C. Le Royer, Y. Morand, S. Maitrejean, J.-M. Hartmann, A. Halimaoui, D. Rouchon, C. Plantier, M. Vinet, "Top Recrystallization of Partially Amorphized SiGe on SOI for sSOI Fabrication", 2015 MRS Spring Meeting & Exhibit, April 6-10, 2015, San Francisco, California. [2] S. Maitrejean, N. Loubet, E. Augendre, P. F. Morin, S. Reboh, N. Bernier, R. Wacquez, B. Lherron, A. Bonnevialle et al., "A New Method to Induce Tensile Stress in Silicon on Insulator Substrate: From Material Analysis to Device Demonstration," ECS Trans., vol. 66, no. 4, pp. 47-56, Mar. 2015. [3] A. Bonnevialle, C. Le Royer, Y. Morand, S. Reboh, J.-M. Pédini, A. Roule, D. Marseilhan, P. Besson, D. Rouchon, N. Bernier, C. Tabone, C. Plantier, M. Vinet, "A New Method to Induce Local Tensile Strain in SOI Wafers: First Strain Results of the "BOX Creep" Technique", Proc. of SSDM 2015, Japan. [4] A. Idrissi-El Oudrhiri, S. Martinie, J-C. Barbé, O. Rozeau, C. Le Royer, M-A. Jaud, J. Lacord, N. Bernier, Y. Morand, L. Grenouillet, P. Rivallin, et al., "Mechanical Simulation of Stress Engineering Solutions in Highly Strained p-type FDSOI MOSFETs for 14-nm Node and beyond", 2015 SISPAD, pp. 206-209.

## From Mismatch to Process Variations A Unified CAD-Compatible Model of Statistically Correlated Variability

Research topics: Mismatch, Across-Chip Variations, Process Variations, Variability Modeling, SPICE

T. Poiroux, P. Scheer (STM), A. Juge (STM), M. Vinet

Partnership: STMicroelectronics Sponsorship: ENIAC-Places2Be

#### **Context and Challenges**

As downscaling of CMOS technologies is pursued, transistor variability remains a critical challenge for digital and analog applications. Therefore, proper compact modeling of the effect of process variations, from local to global scale, on nanoscaled transistors is crucial for computer-aided design (CAD). Today, CAD models of statistical variability are based on Pelgrom's approach, in which two separated components are described: local mismatch sources, featuring extremely small correlation lengths, and large scale process variations, with correlation lengths larger than die size. An extensive literature exists on causes of deviation from this approach. In particular, some variability sources, such as line-edge / linewidth roughness (LER/LWR), require CAD-compatible models able to deal with correlation lengths comparable to device size and to distance between devices. By generalizing Pelgrom's approach to variability sources with arbitrary correlation length, we have developed a simple CAD model that unifies all cases, from local to large-scale variations, in a single formulation

#### **Main Results**

Considering a given process parameter p as variability source, we assume that device characteristics are impacted by the average  $\bar{p}$  of this process parameter over the device area (or over the transistor width if LER is considered), as done in Pelgrom's approach. Without doing any assumption about the process parameter autocovariance function, except that it is monotonically decreasing as the position shift is increased, process parameter power spectral density (PSD) equivalently, autocovariance function) can be decomposed as a sum of centered normal functions. Each of these normal components of the PSD contributes independently (i.e. in an uncorrelated way) to the mismatch induced by process parameter variations. Then, for each normal component, an exact expression of autocovariance function of the averaged process parameter  $\bar{p}$ can be calculated as a function device dimensions  $(D_x, D_y)$ , distance between device centers  $(P_x, P_y)$  and PSD component correlation length  $(\Lambda_{xi}, \Lambda_{yi})$ :

$$\begin{split} \Gamma_{\vec{p}-\langle p\rangle,i}\left(P_{x},P_{y}\right) &= \frac{\alpha_{i}\Lambda_{xi}\Lambda_{yi}}{4D_{x}^{2}D_{y}^{2}} \times \left(\theta\left(\frac{P_{x}+D_{x}}{\Lambda_{xi}}\right) - 2\theta\left(\frac{P_{x}}{\Lambda_{xi}}\right) + \theta\left(\frac{P_{x}-D_{x}}{\Lambda_{xi}}\right)\right) \\ &\times \left(\theta\left(\frac{P_{y}+D_{y}}{\Lambda_{yi}}\right) - 2\theta\left(\frac{P_{y}}{\Lambda_{yi}}\right) + \theta\left(\frac{P_{y}-D_{y}}{\Lambda_{yi}}\right)\right) \end{split}$$

with  $\theta(u)$  the primitive integral of error function erf(u):  $\theta(u) = u \times erf(u) + e^{-u^2}/\sqrt{\pi}$

From this exact calculation of  $\bar{p}$  autocovariance function, we can obtain simple expressions of the variance of device pair mismatch in asymptotic cases of correlation lengths. These asymptotic expressions are summarized in table below.

|                                | $\Lambda_{yi} \ll D_y$                                                                            | $D_y \ll \Lambda_{yi}$                                                                                                            |

|--------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| $\Lambda_{xi} \ll D_x (< P_x)$ | $\frac{2\alpha_i}{D_x D_y}$                                                                       | $\frac{2\alpha_i}{D_x(\sqrt{\pi}\Lambda_{yi})}$                                                                                   |

| $D_x \ll \Lambda_{xi} \ll P_x$ | $\frac{2\alpha_i}{\left(\sqrt{\pi}\Lambda_{xi}\right)D_y}$                                        | $\frac{2\alpha_i}{(\sqrt{\pi}\Lambda_{xi})(\sqrt{\pi}\Lambda_{yi})}$                                                              |

| $(D_x <) P_x \ll \Lambda_{xi}$ | $\frac{2\alpha_i}{\left(\sqrt{\pi}\Lambda_{xi}\right)D_y}\left(\frac{P_x}{\Lambda_{xi}}\right)^2$ | $\frac{2\alpha_i}{\left(\sqrt{\pi}\Lambda_{xi}\right)\left(\sqrt{\pi}\Lambda_{yi}\right)}\left(\frac{P_x}{\Lambda_{xi}}\right)^2$ |

Figure 1:Asymptotic expressions of the variance of mismatch between two identical devices of size  $(D_x, D_y)$ , separated by a center-to-center distance  $P_x$  for a normal component of process parameter of amplitude  $\alpha_i$  and correlation lengths  $(\Lambda_{xi}, \Lambda_{yi})$ .

Based on this analysis and on asymptotic expressions summarized in previous table, we have developed a simple analytical model compatible with implementation in conventional CAD flow for Monte-Carlo simulations. For each independent normal component of the process parameter PSD, this model provides very simple, although very accurate, expressions for single device variance  $\sigma_{\vec{p},i}^2$  and for correlation coefficient between devices  $\rho_i$ :

$$\sigma_{p,i}^{2} \approx \frac{\sqrt{\alpha_{i}}}{\sqrt{D_{x}^{2} + \pi \Lambda_{xi}^{2}}} \frac{\sqrt{\alpha_{i}}}{\sqrt{D_{y}^{2} + \pi \Lambda_{yi}^{2}}}$$

$$\rho_{i} \approx e^{-\pi P_{x}^{2}/(D_{x}^{2} + \pi \Lambda_{xi}^{2})} e^{-\pi P_{y}^{2}/(D_{y}^{2} + \pi \Lambda_{yi}^{2})}$$

Thanks to the normal form of the correlation coefficient, this model can be implemented in conventional CAD environment quite easily. The only requirement is to get device absolute positions (referenced to arbitrary origin) as instance parameters. Then, thanks to the use of these device positions in well-chosen trigonometric expressions, the expected mismatch results, including cases of multifinger transistors, can be obtained from usual Monte-Carlo simulations.

#### **Perspectives**

This approach unifies local mismatch and statistically correlated process variation descriptions in a single formulation, and provides a way to deal with multi-scale variability sources, including sources with significant component at correlation lengths comparable to device dimensions. Therefore, it can be used to describe correctly the effect of pure local mismatch source, large scale process variations, as well as all intermediate cases of variability sources with correlation lengths of the order of magnitude of device dimensions and distance between devices. In particular, this model provides an essential correction to be brought to initial Pelgrom's approach for LER/LWR variability.

#### Related Publications

[1] T. Poiroux, P. Scheer, A. Juge, M. Vinet, "Multiscale statistically correlated variability: A unified model for Computer-Aided Design", *IEEE Transactions on Electron Devices*, Vol. 62, pp. 3605-3612, 2015.

Electron Devices, Vol. 62, pp. 3605-3612, 2015.

[2] A. Juge et al., "Variability at all levels – a challenge for the semiconductor industry", ESSDERC Workshop on Variability, Sept. 2015.

## Tungsten and Copper Interconnection Stability for 3D VLSI CoolCube<sup>™</sup> Integration

Research topics: CMOS, SOI, 3D Sequential, Interconnection

C. Fenouillet-Beranger, S. Kerdilès, F. Deprat, P. Batude, M-P. Samson (STM), B. Previtali, N. Rambal, V. Lapras, L. Emery(STM), C. Euvrard-Colnat, A. Seignard, P. Besson (STM), R. Kachtouli, A. Roman (STM), C. Ribière, V. Lu (STM), L. Brunet, E. Gourvest (STM), G. Druais (STM), Y. Loquet (STM), L. Arnaud, Y. Le-Friec (STM), O. Pollet, V. Benevent, F. Aussenac, H. Denis, V. Jousseaume, S. Maitrejean, M. Vinet

Partnership: STMicroelectronics, IBM, Qualcomm Sponsorship: NANO 2017, EQUIPEX FDSOI11

#### **Context and Challenges**

An alternative approach to conventional device scaling for future nodes is the 3DVLSI or sequential 3D integration [1]. Compared to TSV-based 3D ICs, CoolCube<sup>TM</sup> process flow offers the possibility to stack devices with a lithographic alignment precision (few nm) enabling ultra-high via density. To benefit from the full 3D opportunities and avoid global routing congestion [2], there is a need to implement local routing of the bottom tier: inter-tier metal layers need to be incorporated in the technology (Fig.1). As a consequence, Back End Of Lines (BEOL) levels need to support top FET thermal budgets. A reasonable maximum thermal budget for top FET has been determined around 500°C implying to find solutions for implementing back end material stable beyond 400°C. Currently the combination of copper (Cu) with ULK (Ultra Low-K) materials is widely used for standard BEOL (low resistivity & capacitance, and thus speed improvement). However the integration of such materials in the intermetal levels of a  $CoolCube^{TM}$  integration faces a number of challenges. Indeed Cu metallization can cause contamination issues in the case of wafer break during the process of the top transistor where FEOL contamination environment is required. Despite the fact that its intrinsic resistance is larger, a solution can be the use of tungsten (W) as it has already been integrated in the FEOL of several products.

#### **Main Results**

In order to highlight the interest of W interconnections for 3D  $CoolCube^{TM}$  integration, we have used the standard 28nm design rules damascene BEOL integration of the state of the art FDSOI technology.

Figure 1: 3D VLSI structure with 2 levels of inter-tiers interconnections.

Figure 2: Process flow scheme for BEOL M1 stack and list of annealings applied on Cu or W lines.

Figure 3: Metal 1

TEM cross sections

filled with a) Cu and

b) W before

annealings.

The ULK material is a porous PECVD SiOCH with a k value of around 2.7. For both Cu and W interconnects, only metal 1 (M1) level is integrated. After the TaN/Ta/Copper or TiN/Ti/W

filling, the CMP planarization is realized and a SiCN layer of 20nm is deposited as a capping layer during post-annealings. The different annealings tested on the M1 interconnect are

summarized in Fig.2. Fig.3 shows TEM cross sections of the W (bottom) and Cu (upper) interconnections before anneal.

Fig.4 shows the M1 line resistance measured on a specific multi-fingers/serpentine test structure for Copper and W interconnections before annealing. As expected, the W resistance is a factor 6 higher than the copper one for quasi-similar capacitance values. Finally, the median value of the W line resistance has been extracted and highlights no modification up to 500°C 2h annealing confirming the good thermal W stability (Fig.5). Similar results are obtained for the Cu intercos submitted to post thermal anneals (Fig.6).

Figure 4: Comparison of Cu and W M1 intercos before annealings for a line width and space of 45nm.

Figure 5: W resistance evolution before and after annealings.

Cu resistance (no anneal) as reference.

Figure 6: Cu M1 line resistance versus post thermal anneallings.

Thanks to morphological and electrical characterization for a 28nm design rules technology, Cu and W interconnections stability is highlighted up to 500°C 2h and 550°C 5h respectively [3]. Regarding dielectric, a slight performance degradation has been evidenced by our study, it was unexpected for ULK film if we refer to literature data. Regarding metals, no performance degradation was observed. Therefore this study should be completed by investigation of the reliability of the dielectric and of the integrated W and Cu interconnects.

#### **Perspectives**

In order to tackle the W BEOL metallization resistance penalty as compared to copper and to improve the capacitance stability, some alternative materials are under study. For example lower resistivity metal material coupled with  $SiO_2$  or non-porous low-k materials could be envisaged to push forward the top tier thermal treatment limitation.

#### Related Publications

- [1] P. Batude *et al*, "3DVLSI with CoolCube process: An alternative path to scaling", 2015 Symposium on VLSI Technology, June 16-19, 2015, Kyoto, Japan. [2] O. Billoint *et al*, "A Comprehensive Study of Monolithic 3D Cell on Cell Design Using Commercial 2D Tool", *Design, Automation and Test in Europe (DATE 2015)*, March 9-13, 2015. Grenoble, France.

- [3] C. Fenouillet-Beranger et al, International Conference on Solid State Devices and Materials (SSDM 2015), Sept. 27-30, 2015, Sapporo, Japan.

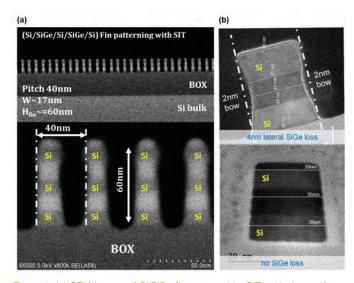

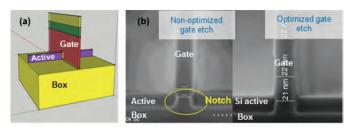

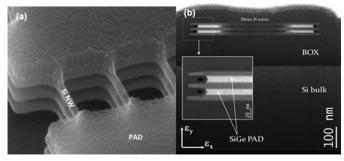

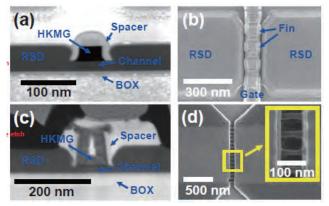

#### Nanowire MOSFET for 5nm Node and Beyond

Research topics: CMOS, SOI, Nanowire, Advanced Patterning

S. Barraud, V. Lapras, L. Gaben, M.P. Samson (STM), M. Cassé, J.M. Hartmann, C. Vizioz, C. Arvet (STM), P. Pimenta-Barros, V. Loup, F. Glowacki, V. Maffini-Alvaro, L. Grenouillet, Y. Morand (STM), N. Bernier, O. Rozeau, M.A. Jaud, S. Martinie, J. Laccord, M. Vinet

Partnership: STMicroelectronics, IBM, SOITEC Sponsorship: NANO 2017, EQUIPEX FDSOI11

#### **Context and Challenges**

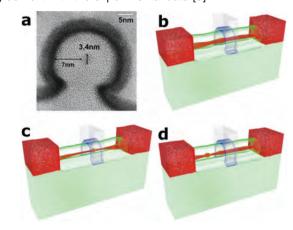

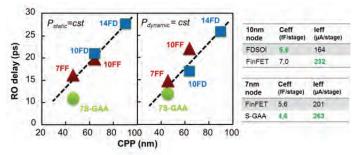

For many years, semiconductor nanowires (NWs) have offered the prospect of enabling the next generation of MOSFET devices for digital circuits. These 1D nanostructures, with optimal electrostatic confinement and consequently significant short-channel effect benefits, are often considered as the "ultimate CMOS devices". If promising preliminary developments have been carried out in order to establish a NW-based CMOS technology platform, many open questions still remain in order to address the 5nm node and beyond. During this year the "NW team" focused its work on electronic transport properties (impact of NW size and substrate orientation) in NWs, the benchmarking of stacked-NWs with FinFET, and the main challenges for the fabrication of stacked-GAA NWs.

#### **Main Results**

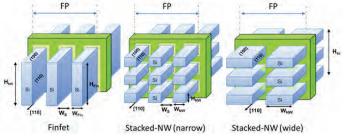

For 5nm node and beyond. NW-based transistors are today considered as a credible alternative to FinFET (FF) technology. However, it still remains unclear if, using the same technology constraints as for FinFET, stacked-NW devices are actually able to overcome FF performances in advanced CMOS technologies. To find answers, 3D TCAD simulations have been performed in order to benchmark the performances of stacked-NWs with FinFET and to define guidelines for 5nm node. The results of TCAD simulation allow us to know the NW dimensions (width and height) required to overcome FinFET performances for a given footprint (Fig.1). The comparison is done by assuming the same space between Fin or stack (W<sub>S</sub>) and the same total thickness ( $H_{tot}$ ). Operating voltage was  $V_{DD}$ =0.7V and the gate length has been fixed at L<sub>G</sub>=16nm. In both cases, the use of wide NWs leads to increase the effective width (Weff) as compared to FF which is a key element for improving performances. Similarly to FF, the stacked-GAA NWs configuration shows a DIBL~60mV/V but with higher Weff.

Figure 1: Schematics of FinFET, narrow stacked-GAA nanowires and wide stacked-GAA nanowires (also named "nanosheets").

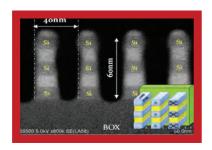

Figure 2: (a) (SiGe/Si) superlattice epitaxial growth, (b) Fin patterning by SIT (FP=40nm), (c) Selective etching of SiGe versus Si in order to release Si NWs, (d) Cross-sectional TEM image of 3D stacked-NWs.

It was shown that a significant delay reduction (>20%) can be obtained by using stacked-GAA NW technology (also named "nanosheets") for wide (>20nm) and thin NWs ( $T_{Si}$ =7nm). The delay reduction is explained by their increased effective width and limited parasitic capacitances within a given footprint.

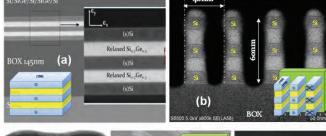

After this first study on the design of stacked-NWs, the main challenges for the fabrication of stacked-NWs have been addressed. A replacement metal gate (RMG) integration scheme has been developed for stacked-NWs on SOI substrates including the following process steps (Fig.2); (i) an epitaxial growth of (Si/SiGe)<sub>xN</sub> superlattice with strained-Si channel for NFET and compressive SiGe channel for PFET, (ii) advanced patterning (Sidewall-Image-Transfer technique) for the definition of (Si/SiGe)<sub>xN</sub> Fins (Fin width=17nm with a 40nm Fin pitch), (iii) an inner spacers module in order to reduce the parasitic capacitances and (iv) the selective etching of SiGe (versus Si) to preserve Si channels after the dummy gate removal.

#### **Perspectives**

The perspective of this work is to develop dual-channel CMOS co-integration with Si NFET and strained-SiGe PFET in stacked-GAA nanowire device architectures.

#### Related Publications

[1] L. Gaben, S. Barraud, M.-A. Jaud, S. Martinie, O. Rozeau, J. Lacord, G. Hiblot, S. Monfray, F. Bœuf, T. Skotnicki, F. Balestra, M. Vinet, "Stacked-NW and FinFET transistors: guidelines for the 7nm node", *International conference on Solid State Devices and Materials (SSDM 2015)*, Sept. 27-30, 2015, Sapporo, Japan

[2] L. Gaben, S. Barraud, P. Pimenta-Barros, Y. Morand, J. Pradelles, M.-P. Samson, B. Previtali, P. Besson, F. Allain, S. Monfray, F. Bœuf, T. Skotnicki, F. Balestra, M. Vinet, "Ω-Gate NW transistors realized by sidewall image transfer patterning: 35nm channel pitch and opportunities for stacked-NWs architectures", International conference on Solid State Devices and Materials (SSDM 2015), Sept. 27-30, 2015, Sapporo, Japan.

## 02 MEMORIES

- Impact of MOX/Al2O3 CBRAM Bilayer Structure on Window Margin and Memory Reliability for NVM Applications

- Operation Fundamentals in 12Mb Phase Change Memory Based on Innovative Ge-rich GST Materials Featuring High Reliability Performance

- The Physical Mechanisms Involved in Resistive Memories Clarified by Advanced Studies on the Structure of Amorphous Chalcogenides

- Potentialities of Vertical Resistive RAM (VRRAM) for Neuromorphic Applications

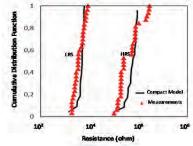

## Impact of MOX/Al<sub>2</sub>O<sub>3</sub> CBRAM Bilayer Structure on Window Margin and Memory Reliability for NVM Applications

Research topics: CBRAM, NV Memory, Metal-Oxide, Bilayer, Embedded Applications

M. Barci, G. Molas A. Toffoli, M. Bernard, A. Roule, C. Cagli, E. Vianello, B. De Salvo, L. Perniola

#### Sponsorship: ENIAC-PANACHE

#### **Context and Challenges**

Conductive Bridge RAM (CBRAM) is presented as a promising candidate to replace the Flash memory due to CMOS compatibility, high operational speed at low voltages, low operating current and good thermal stability. Its basic working principle relies on the formation and dissolution of a conductive layer sandwiched filament in a resistive between electrochemically reactive and inert electrodes. temperature stability [1,2], large window margin and good endurance are required for advanced non-volatile memory applications. In this work, we propose an optimized Al<sub>2</sub>O<sub>3</sub> 0.5nm/MO<sub>X</sub> 4nm bilayer oxide-based CBRAM [3] in order to improve the memory performances (memory window, thermal stability and endurance).

#### **Main Results**

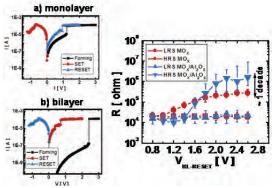

In Fig.1 (left) are presented typical IV characteristics of monolayer (a) and bilayer (b) CBRAM devices. Forming voltage of bilayer is almost 1V bigger than monolayer. In Fig.1 (right)  $R_{\text{OFF}}$  evolution is shown as the bit line (|VBL-RESET|) voltage is increased for different SET conditions (in terms of  $V_{\text{WL}},\,V_{\text{BL-SET}}$  and  $P_{\text{W}}).$  Between each RESET operation, the CBRAM is set back to the ON state. As  $V_{\text{RESET}}$  is increased, RESET saturates for monolayer and  $R_{\text{OFF}}$  reaches a limit of  $\sim 2.10^5~\Omega.$  On the contrary, for the bilayer,  $R_{\text{OFF}}$  continues to increase and  $10^6~\Omega$  can be attained at  $V_{\text{BL-RESET}}{=}2.2\text{V}.$  In other words, despite a slower initial RESET process in double layers (lower RESET speed), a higher  $R_{\text{OFF}}$  can be reached due to a higher  $R_{\text{OFF}}$  after saturation.

Figure 1: (left) Typical IV characteristics for mono and bilayer CBRAM devices. (right)  $R_{\text{OFF}}$  as a function of RESET |VBL| voltage (1 $\mu$ s pulses) for the studied samples.  $R_{\text{ON}}$  between each RESET cycle is also represented.

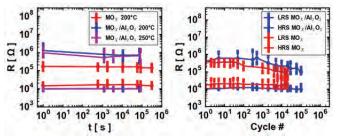

Fig.2 (left) presents the retention behavior of the monolayer and bilayer structures at 200°C at 250°C for 24 hours. We can observe that the window margin gain obtained with bilayers remains stable over time, highlighting the good

thermal stability of this technology. In Fig.2 (right) are presented the endurance characteristics of monolayer and bilayers. In the case of bilayer  $Al_2O_3/MO_X$ , a clear improvement is demonstrated, with  $10^5$  cycles maintaining constant a window margin of 1 decade.

Figure 2: (left) Data retention behavior of monolayer and bilayer devices up to 250°C/24hrs. (right) Endurance behavior for monolayer (red) and bilayer (blue) devices up to 10° cycles.

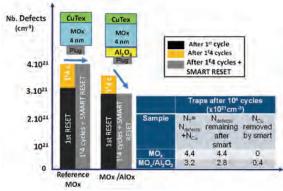

In Fig.3, based on the TAT model, we estimated the trap and Cu contributions to the  $R_{\text{OFF}}$  drift by comparing the  $R_{\text{OFF}}$  values after cycling with and without final smart RESET (progressive increase of  $V_{\text{BL-RESET}}$  until  $R_{\text{target}}$  is reached). Al<sub>2</sub>O<sub>3</sub>/MO<sub>X</sub> bilayer reduces the generated trap density of 50% compared to the monolayer reference, explaining the improved reliability performances.

Figure 3: Slopes ( $v_{\rm ON}$  and  $v_{\rm OFF}$ ) of LRS (square) and HRS (circle) as a function of the  $l_{\rm SET}$  used to set the initial  $R_{\rm ON}$  during retention at 130°C. Endurance behavior for monolayer (red) and bilayer (blue) devices up to  $10^5$  cycles.

#### **Perspectives**

Bilayer Cu-based/MO $_{\rm X}/{\rm Al_2O_3}/{\rm metal}$  plug CBRAM devices show improved reliability performances in terms of retention (250°C/24hrs) and endurance behavior (~1 decade at 10 $^{\rm 5}$  cycles), confirming to be a promising technology for potential future high density memory applications.

#### Related Publications

[1] M. Barci, J. Guy, G. Molas, E. Vianello, A. Toffoli, J. Cluzel, A. Roule, M. Bernard, C. Sabbione, L. Perniola B. De Salvo, "Impact of SET and RESET conditions on CBRAM high temperature data retention", 2014 IEEE International Reliability Physics Symposium, pp. 5E-3, 2014.

[2] G. Molas, E. Vianello, F. Dahmani, M. Barci, P. Blaise, J. Guy, A. Toffoli, M. Bernard, A. Roule, F. Pierre, C. Licitra, B. De Salvo, L. Perniola, "Controlling oxygen

(2) G. Molas, E. Vianello, F. Dahmani, M. Barci, P. Blaise, J. Guy, A. Toffoli, M. Bernard, A. Roule, F. Pierre, C. Licitra, B. De Salvo, L. Perniola, "Controlling oxygen vacancies in doped oxide based CBRAM for improved memory performances", 2014 IEEE International Electron Devices Meeting, pp. 6-1, 2014.

[3] M. Barci, G. Molas, A. Toffoli, M. Bernard, A. Roule, C. Cagli, J. Cluzel, E. Vianello, B. De Salvo, L. Perniola, "Bilayer Metal-Oxide CBRAM Technology for Improved Window Margin and Reliability", 2015 IEEE International Memory Workshop (IMW), pp. 1-4, 2015.

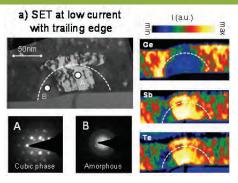

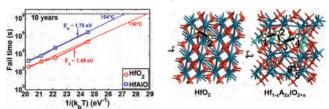

## Operation Fundamentals in 12Mb Phase Change Memory Based on Innovative Ge-rich GST Materials Featuring High Reliability Performance

Research topics: Phase Change Memories, High Temperature Data Retention, Phase Field Modeling

V. Sousa, O. Cueto, G. Navarro, N. Castellani, M. Coué, V. Delaye, C. Sabbione, P. Noé, F. Fillot, L. Perniola, S. Blonkowski, P. Zuliani, R. Annunziata

Partnership: STMicroelectronics Sponsorship: ENIAC-PANACHE

#### **Context and Challenges**

Phase-Change Memories (PCM) are today considered the most mature among novel non-volatile memory technologies. Recent results have highlighted an optimized Ge-rich GeSbTe (GST) phase change material, which is able to guarantee code integrity after soldering thermal profile and data retention in extended temperature range. Our work presents the performances of ±2at% Ge concentration around the optimized material when integrated on a 12Mbits test vehicle [1]. In order to simulate the electro-thermal characteristics of our devices and to reproduce the phase change mechanisms of the PCM material during the set and reset operations, we have developed a finite element electro-thermal solver coupled with the Phase Field Method [2]. The confrontation of the experimental observations to the simulation results allowed us to achieve the understanding of the origin of the high thermal stability of the two programmed states.

#### **Main Results**

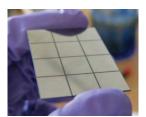

In our study, the Ge-rich GST phase change materials have been fabricated by magnetron sputtering and integrated in state-of-the-art PCM devices. The SET/RESET distributions of the 12Mb test vehicle (Fig.1) show that the reading window is preserved after a 2h bake at 230°C for all the evaluated Ge contents in the range of  $\pm 2$ at% from the optimized alloy, thus illustrating the high thermal stability of the programed states and the large process window of the material.

Figure 1: Micrograph of the 12Mbits test vehicle and SET/RESET distributions after a 2h bake at 230°C for Ge-rich GST alloys with Ge variations of ±2at% wrt the optimized alloy, demonstrating the large process window.

Figure 2: Superimposition of the BF/DF images and STEM/EELS signal for the SET states of GST+Ge45% devices programmed at low current: a crystalline column of single orientation is formed across the active area while the elemental distribution reveal the depletion in Germanium at the core of the cell.

The composition analysis performed by EELS at the core of the storage element (Fig.2) shows how the initially high Ge content allows retaining a Ge-rich alloy at the core of the cell, although a strong segregation effect tends to expel Ge out of the active area, thus explaining the high thermal stability of the RESET state wrt crystallization. The peculiar grain structure imaged by TEM allows us to correlate the low drift of the SET state operated at low current with the low number of amorphous-like grain boundaries standing along the conduction path. The simulation results obtained thanks to the phase field method (Fig.3) show how this crystalline structure is the result of the growth of the top crystal grain during programming.

Figure 3: Simulation using the phase field method of the phase change during the SET operation at low current.

#### **Perspectives**

The introduction of the multi-phase field method in the simulation tool will enable to give account not only for the phase change during programming, but also for the evolution of the grain structure and the elemental segregation.

#### Related Publications

[1] V. Sousa, G. Navarro, N. Castellani, M. Coué, O. Cueto, C. Sabbione, P. Noé, L. Perniola, S. Blonkowski, P. Zuliani, R. Annunziata, "Operation Fundamentals in 12Mb Phase Change Memory Based on Innovative Ge-rich GST Materials Featuring High Reliability Performance", *Proceedings of the VLSI conference* (2015)

[2] O. Cueto, V. Sousa, G. Navarro and S. Blonkowski, "Coupling the Phase-Field Method with an Electrothermal Solver to Simulate Phase Change Mechanisms in PCRAM Cell", *Proceedings of the SISPAD conference* (2015).

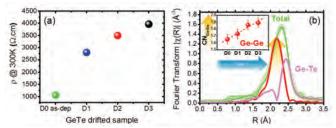

#### The Physical Mechanisms Involved in Resistive Memories Clarified by Advanced Studies on the Structure of Amorphous Chalcogenides

Research topics: Chalcogenide, ReRAM, PCRAM, CBRAM, Amorphous Structure

P. Noé, E. Souchier, C. Sabbione, M. Bernard, V. Jousseaume, P. Blaise, N. Castellani, G. Veux, G. Navarro, V. Sousa, F. Hippert (LNCMI), F. D'Acapito (CNR)

Partnership: CRG Beamline LISA/CNR-IOM-OGG c/o ESRF, CNRS-LNCMI Sponsorship: ANR-SESAME, ENIAC-PANACHE

#### **Context and Challenges**

Chalcogenide-based resistive random access memories (mainly Phase Change and Conductive Bridging RAM) are considered as the most promising emerging technologies for the next generation of non-volatile memory. Both of these memories involves a chalcogenide compound which can be electrically switched between two reversible and distinct resistance states. In PCRAM, a Te-based phase-change alloy is reversibly switched electrically between its amorphous and crystalline states which present a very high contrast in resistivity. Whereas, in CBRAM devices, it is supposed that ions are produced at an electrochemically active anode and migrate in the chalcognenide electrolyte to form a conducting path under the influence of an electric field. This process is reversible by applying an opposite bias. However, such technologies have to face major technological challenges that have prevented or delayed up to now their successful transfer to industry.

#### Resistance drift phenomenon in PCRAM

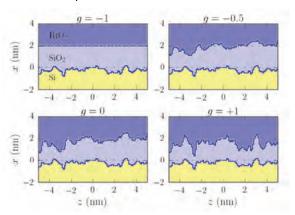

One of the main challenge for PCRAM technologies concerns the so-called resistance drift phenomenon. The drift is characterized by a spectacular increase of the resistance with ageing of the amorphous (a-) phase of the phase-change chalcogenide alloy. It is commonly attributed to a structural relaxation, the nature of which remains unknown, and has until now hindered the development of ultra-high multilevel storage devices with multi-level cell operation (MLC).

Figure 1: (a) Resistivity ρ measured at 300 K on a prototypical a-GeTe sample in as-deposited (D0) state and set at different ageing and resistance drift levels (D1, D2 and D3). (b) Fourier transform (squares) with best fit curve (continuous lines) of the EXAFS spectrum of sample D0 showing partial contribution of Ge-Ge and Ge-Te bonds. The insert is a plot of the change in Ge-Ge coordination number deduced from analysis of EXAFS data of D0 to D3 samples showing the increase in Ge-Ge homopolars bonds with drift.

In that context, we experimentally evidenced for the first time a direct structural change with resistance drift in prototypical a-GeTe thin film by grazing incidence x-ray absorption spectroscopy (GIXAS) [1]. Different pieces of the a-GeTe film were set at different resistance drift levels by thermal annealing prior to the XAS experiment at the Ge K-edge (Fig.1(a)(b)(c)). In all samples, Ge-Ge and Ge-Te bonds coexist (Fig.1(d)). Nevertheless, this study demonstrates that the drift phenomenon is concomitant to a clear change in the local Ge environment: the number of Ge-Ge homopolar bonds increases as the resistance increases (Fig.1(d)), which is contrary to current theoretical predictions in the literature.

This effect could be related to a decrease of defect states and increase of trap states in the band gap, induced by the structural changes, leading to a progressive increase in resistivity of the amorphous semiconductor. In any case, the impact of the observed structural changes will have to be taken into account in models in order to definitively conclude on the origin of drift phenomenon and are of major importance in designing phase change materials that exhibit very low resistance drift in the amorphous phase in order to develop MLC PCRAM.

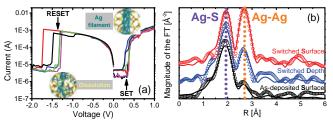

#### Resistive switching mechanism of CBRAM

The major limitation of CBRAM is related to the poor stability of the conductive filament in the amorphous chalcogenide highlighting the lack of understanding of the switching mechanism at the nanoscale level preventing thus successful transfer to industry.

Figure 2: (a) Typical I(V) curves of a CBRAM device to be analyzed by XAS during cycles of SET and RESET between the low and high resistive states. The inserts are the schematic drawing of a silver nano-filament in GeSx and the silver filament dissolution scheme. (b) Fourier Transforms of EXAFS spectra at Ag K-edge of 3 prototypical samples (switched CBRAM using surface and depth collection mode and a non-switched CBRAM on the surface) with the best fit curves (continuous lines). The vertical arrows mark the features that grow with increasing Ag-metal content.

Our approach was based on CBRAM devices specifically designed in order to be finely characterized depending on their resistive states by means of depth-selective X-ray absorption spectroscopy (XAS) [2]. The Ag/GeSx/W CBRAM devices are analyzed using depth selective X-ray Absorption Spectroscopy before and after switching. Fig.1(a) illustrates the typical I(V) curves obtained and the reversible switching from the high to the low resistive state (SET and RESET, respectively). The study of the local environment around Ag atoms in such devices reveals that Ag is in two very distinct environments with short Ag-S bonds due to Ag dissolved in the GeSx matrix, and longer Ag-Ag bonds related to an Ag metallic phase. These experiments allow the conclusion that the switching process involves the formation of metallic Ag nano-filaments initiated at the Ag electrode. All these experimental features are well supported by ab initio molecular dynamics simulations showing that Ag favorably bonds to S atoms, and permit the proposal of a model at the microscopic level that can explain the instability of the conductive state due to progressive sulfidation of metallic Ag in these Ag-GeSx CBRAM devices. Finally, the principle of the nondestructive method described here can be extended to other types of resistive memory concepts.

#### Related Publications

[1] P. Noé, C.Sabbione, N. Castellani, G. Veux, G.Navarro, V. Sousa, F. Hippert and F. d'Acapito, "Structural change with the resistance drift phenomenon in amorphous GeTe phase change materials' thin films", J. Phys. D: Appl. Phys. 49, 035305 (2016).

[2] E. Souchier, F. d'Acapito, P. Noé, P. Blaise, M. Bernard and V. Jousseaume, "The role of the local chemical environment of Ag on the resistive switching

mechanism of conductive bridging random access memories", Phys. Chem. Chem. Phys. 17, 23931 (2015).

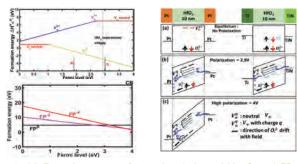

#### Potentialities of Vertical Resistive RAM (VRRAM) for Neuromorphic Applications

Research topics: OxRAM based VRRAM for Neuromorphic

Authors: G. Piccolboni, G. Molas, J. M. Portal, R. Coquand, M. Bocquet, D. Garbin, E. Vianello, C. Carabasse, V. Delaye, C. Pellissier, T. Magis, C. Cagli, M. Gely, O. Cueto, D. Deleruyelle, G. Ghibaudo, B. De Salvo, L. Perniola

#### Sponsorship: ENIAC-PANACHE

#### **Context and Challenges**

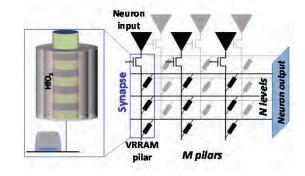

Combining Resistive RAM concept with Vertical NAND technology and design, Vertical RRAM (VRRAM) was recently proposed as a cost-effective and extensible technology for future mass data storage applications. 3D RRAM based neural networks were also proposed to emulate the potentiation and depression of a synapse, but more complex circuits were not discussed. In previous works [3-4], various RRAM based neuromorphic circuits were proposed and investigated, using planar devices.

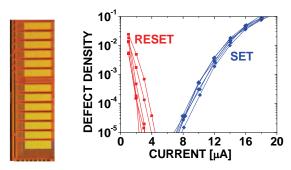

#### **Main Results**

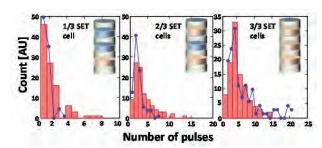

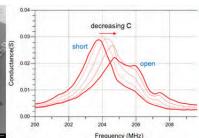

Vertical RRAM were fabricated (Fig.1) and investigated obtaining promising results (20ns switching time, up to 10' cycles and stable 200°C retention). VRRAM was then proposed as a solution to increase the density of neuromorphic circuits thanks to the staking of memory cells and the reduced use of transistors. 1TnR pillars are proposed to emulate synapses (Fig.2). For cochlea application [3,4], good agreement with planar binary OXRAM configuration with random generator is obtained (Fig.3), with an area gain of more than a factor 3. Resistance correlation between adjacent cycles improves the reliability for neuromorphic applications requiring low endurance performances. Thus, for convolutional neural network, 10-15 RRAM levels are sufficient to reach a recognition rate of more than 98%. VRRAM based synapses open the path to high-density neuromorphic circuits requiring aggressive synaptic levels.

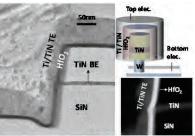

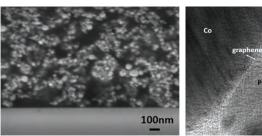

Figure 1: Description of the integration flow, and TEM cross sections (high resolution and dark field) of the TiN/HfO2/Ti/TiN VRRAM.

Figure 2: Simulated neuromorphic network. A synapse is composed by N VRRAM cells in a pillar addressed in parallel. The output neuron collects the contributions of all synapses.

Figure 3: Cochlea application: circuit simulated with synapses composed of 3 stacked VVRAM. SET conditions are fixed to target 20% of occurrence probability (fig. 19). Distributions of required # of pulses to SET respectively 1, 2 or 3 cells per pillar are represented and compared with a theoretical case.

#### **Perspectives**

The following step in the process/integration is to perform electrical characterization on 2-level VRRAM, comparing the 2 levels. Concerning the design a more detail study is needed to properly dimension all the circuital components in order to verify the limitations (max number of levels, etc.) for our neuromorphic solution.

#### **Related Publications**

- [1] G. Piccolboni *et al.*, "Investigation of the Potentialities of Vertical Resistive RAM (VRRAM) for Neuromorphic Applications", *IEDM Tech. Digest, 2015...* [2] G. Piccolboni *et al.*, "Investigation of HfO2/Ti based vertical RRAM Performances and variability", *2014 NVMTS Tech. Dig.* pp.1-5.

- [3] M. Suri et al., "CBRAM devices as binary synapses for low-power stochastic neuromorphic systems: auditory (cochlea) and visual (retina) cognitive processing applications", IEDM 2012 Tech. Dig., pp.235-238.

- [4] D. Garbin et al., "Variability-tolerant Convolutional Neural Network for Pattern Recognition Applications based on OxRAM Synapses", IEDM Tech. Dig., 2014.

## 03 PATTERNING

- Mask-Less Lithography for Advanced CMOS Technology

- NanoImprint Lithography Industrial Platform Assessment within INSPIRE

- DSA Integration Challenges for Contact Hole & Via Patterning

- Computational Aspects of Lithography

- Advanced Patterning of Stacked Nanowires Transistor

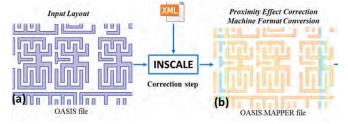

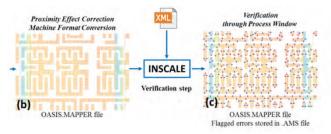

#### Mask-Less Lithography for Advanced CMOS Technology

Research topics: Advanced Lithography, Data Preparation, Lithography Process, Resist Outgassing

L. Lattard, S. Berard Bergery, Y. Blancquaert, B. Dalzotto, L. Dubus, K. Lepinay, M.L. Pourteau, J. Pradelles, G. Rademaker, I. Servin

Partnership: MAPPER Lithography, TSMC, STMicroelectronics, NISSAN Chemical, ASELTA Nanographics, Mentor Graphics, SOKUDO, TEL, Nova

Sponsorship: IMAGINE Program

#### **Context and Challenges**

With the recurrent introduction delay of EUV lithography for High Volume Manufacturing and its constant increasing cost of ownership, mask less lithography (MLL) remains a credible alternative to answer to CMOS manufacturing industry expectations thanks to its cost attractiveness, its intrinsic resolution capability and the high-throughput of the massively parallel writing concept. Since 2009, Leti launched the collaborative program "IMAGINE" to push the insertion of the Mask Less Lithography approach developed by MAPPER lithography (Netherlands).

After technology demonstration achieved on pre-alpha tool in Leti, Mapper lithography introduced a new pre-production 300mm technological platform compatible with CMOS 28/20/14 nm technologies. Mapper and Let are now working together for qualification of this new platform.

#### **Main Results**

Several new part of the electronic optic were installed in the tool FLX-1200 at Leti. Please refer to Fig.1.

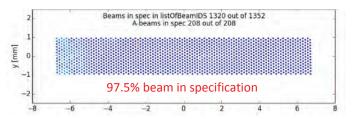

A new version of the so-called Individual Beam Corrector which allow to align individually the 1300 beams. On Fig.2 alignment results are plotted and we were able to demonstrate that 97% of the beams are in specification for alignment of the optical column [1].

Figure 1: Picture of the complete electronic optic of the FLX-1200 tool.

Figure 2: Results of the alignment off all 1352beams inside Electronic optic.

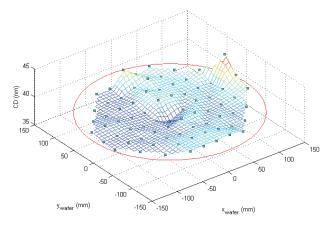

Our greatest achievements in 2015 are the demonstration of a CDU for one beam over a complete 300mm wafer of 2nm (3 sigma) in agreement with the requirement of semiconductor industry for a 28nm technology node with measurement on a 42nm Half Pitch features [2].

Figure 3: Picture of the Critical Dimension Uniformity on 300mm wafer.

#### **Perspectives**

The main 2016 objectives is the qualification of the blanker module which is now in qualification at Mapper Lithography (Netherlands). This blanker module is the cornerstone for Direct Writing lithography tool. This will allow all types of printing features with upload of the design files directing on the wafer thanks the blanker module.

[1] J. Pradelles, J. Reche, Y. Blancquaert, C. Constancias, L. Lattard, N. Vergeer, Y. Ma, P. Wiedemann, G. de Boer, M. Wieland, "Multiple e-beam direct write enters pre-production mode", *Proc. SPIE*, 2015.

[2] G. De Boer, M.P. Dansberg, R. Jager, J.J.M. Peijster, E. Slot, S.W.H.K. Steenbrink, L. Lattard, L. Pain, M.J. Wieland, "Performance validation of MAPPER's FLX-1200", *9423-34*, *Proc. SPIE*, 2015.

#### NanoImprint Lithography Industrial Platform assessment within INSPIRE

Research topic: Nano Imprint Lithography, INSPIRE

H. Teyssedre, M. Louro, S. Landis

#### Partnership: EVG

#### **Context and Challenges**

Nanoimprint techniques stick out from other conventional lithography processes because fundamental mechanism of creating the structures. In classical approaches, they are created through a chemical contrast. In the case of NanoImprint, the contrast is topographic and the flow of the resist through the stamp's cavities shapes the pattern. As during the last decades, significant efforts have been made to overcome the contact between the photomask and the resist coated wafer (to limit defectivity and enhance the resolution), NIL technology appeared to be for many years an UFO, since the process is based on the intimate contact between the working stamp and the resist to be embossed.

In twenty years, consequent technical developments have been achieved to make the technology more mature and ready for high volume manufacturing. Even a plenty of technology alternatives were proposed, the UV based imprint, using transparent stamp, became the standard technology. Two well established options are now available on the market: the full wafer imprint (the size of the stamp correspond to the size of the wafer to be printed) and the step and flash imprint were a small stamp (i.e. die size) is stepped like in optical lithography across the wafer to be processed.

If the step and flash technology is more prone to address the semiconductor markets (NAND Flash memory, DRAM and logic) with high requirement levels for alignment capability and defectivity density, the full wafer option seems to be the reference for the emerging and growing markets like LED and Photonics based devices [1]. The wafer scale imprint solution, much cheaper than the step and flash option, however still lacks from quantitative data regarding technology assessment for high volume manufacturing. Commercially available equipment and resist cornerstones of this technology, however some blocs of a full supply chain (design rules, master manufacturing and repair, in line metrology, integration solutions) need to be established and qualified to make the technology mature enough to rapidly meet market's needs.

#### **Main Results**

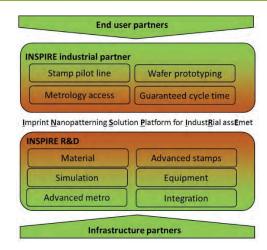

To accelerate this technology adoption Leti and EV Group launched a new program [2] called INSPIRE (see Fig.1) to demonstrate the benefits of NIL technology and spread its use for applications beyond semiconductors. Much more than an industrial partnership, the INSPIRE program is designed to demonstrate the technology's cost-of-ownership benefits for a wide range of application domains, by supporting the development of new applications from the feasibility-study stage to the first manufacturing steps and transferring integrated process solutions to their industrial partners, thus significantly lowering the entry barrier for adoption of NIL for manufacturing novel products.

Figure 1: INSPIRE program organization and philosophy.

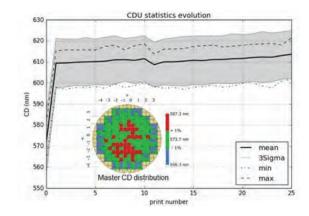

This program focused first on Critical Dimension uniformity (see Fig.2) as well as defectivity assessments onto 200 mm wafers printed with the smart NIL© technology available in the HERCULES® NIL equipment platform. The work brings focus on sub micrometer resolution features fully covering 200 mm silicon master. Repeatability tests were performed over more than 100 printed wafers to collect statistics within a wafer and also wafer to wafer.

#### **Perspectives**

Further technology assessments are already planned within the INSPIRE project. They will help us to propose new development to make the technology more mature and to qualify this solution with respect to customers' needs already involved in the project.

Figure 2: CD-SEM characterization of the feature size distribution 25 200 mm wafers printed with the smart NIL© technology available in the HERCULES® NIL equipment platform. The value are measured over 208 sites on each wafer.

#### Related Publications

[1] L. Pain, R. Tiron, L. Lattard, S. Landis, C. Laviron, "Lithography alternatives: Why are they essential?", *Solid State Technology*, September 2015. [2] S. Landis, H. Teyssedre, L. Pain, "NIL for industrial early adopters, INSPIRE project", *NIL Industrial Day* Berlin 2015.

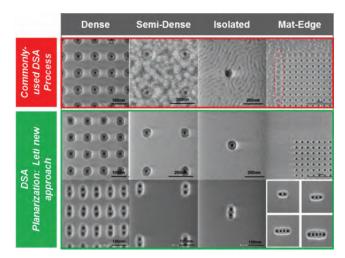

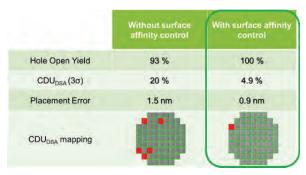

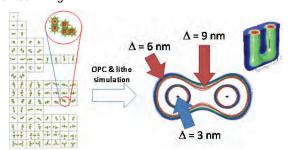

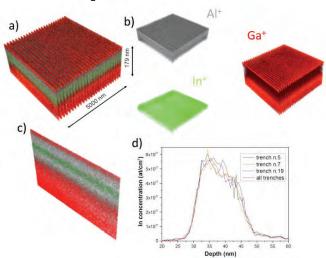

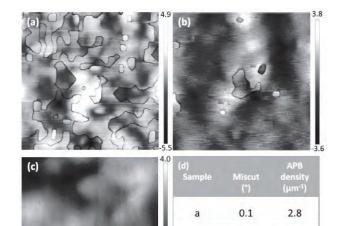

#### **DSA Integration Challenges for Contact Hole & Via Patterning**

Research topics: Advanced Lithography, Directed Self-Assembly, Block-Copolymers, DSA planarization

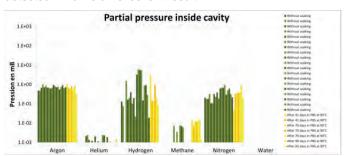

R. Tiron, A. Gharbi, M. Argoud, P. Pimenta-Barros, I. Servin, G. Chamiot-Maitral, A. Sarrazin, C. Lapeyre, S. Bos, S. Bouanani<sup>2</sup>, X. Chevalier<sup>1</sup>, C. Nicolet<sup>1</sup>, C. Navarro<sup>1</sup>